Release Date: 09/18/2020

# **Quad Port TSN Gigabit Ethernet PCIe NIC Card**

The AXM57104 is a 4-port TSN Gigabit Ethernet PCI Express network interface card, compliant to PCI Express base spec. v2.1 Gen1, which supports enhanced TSN functions included the timing and synchronization compliant to IEEE 802.1 AS-Rev/AS and IEEE 1588V2, the Credit-Based Shaper (CBS) compliant to IEEE 802.1Qav, the Time-Aware Shaper (TAS) compliant to IEEE 802.1Qbv, and the Per-Stream Filtering and Policing (PSFP) compliant to IEEE 802.1Qci. AXM57104 also supports 32 synchronous I/O pins, one Pulse Per Second (PPS) output, FPGA hard-core field upgradable via In Application Programming (IAP) for TSN standards evolution.

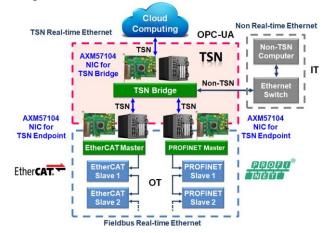

The AXM57104 is a cost-efficient PCIe to TSN solution for Industrial Internet of Things (IIoT) applications to enable TSN functions on industrial automation platforms, Fieldbus over TSN gateways and converge the non-real-time IT (Information Technology) network and real-time OT (Operation Technology) networks which work on different industrial Ethernet protocols such as EtherCAT/PROFINET/EtherNet IP/etc.

### **Key Features**

- Compliant to PCI Express base spec. v2.1 Gen1

- PCIe Network Interface Controller (NIC)

- Gigabit Ethernet Network Interface Controller

- Ethernet packet through Bus-Master DMA

- Unicast/multicast/broadcast filters

- Support Legacy and MSI interrupt

- TSN Gigabit Ethernet Switch

- Support TSN Timing and Synchronization for Time-Sensitive Applications compliant to IEEE 802.1AS-Rev/AS, and IEEE 1588V2

- Support TSN Forwarding and Queuing of Time Sensitive Streams (FQTSS): Specifies Credit-Based Shaper (CBS) compliant to IEEE 802.1Qav

- Support TSN Time-Aware Shaper (TAS) compliant to IEEE 802.1Qbv

- Support TSN Per-Stream Filtering and Policing (PSFP) compliant to IEEE 802.1Qci

- 4 Gigabit Ethernet SGMII interfaces

- Port-based and 802.1Q tag-based VLANs

- Support 8 priority queues

- QoS according to the PCP bits (802.1p), or Ethertype

- Support Independent VLAN Learning (IVL)

- DSA (Distributed Switch Architecture) for frame tagging

- Shared Dynamic and Static MAC Table (4096 entries), Automatic MAC addresses learning and ageing

- Broadcast storm protection and multicast frames filtering

- Per-port Frame rate limiting and Frame/Error counters

- 16 Kbytes packet buffer per port

- FPGA hard-core field upgradable via In Application Programming (IAP) for TSN standards evolution

- Support Board Support Package (BSP)

- 32 Synchronous I/O pins and one I2C master

- One Pulse Per Second (PPS) output

- Support PCI Express x1 slot, Standard profile bracket

- Operating Temperature Range: -40 to +85°C

#### **Block Diagram** PCIe Bus AXM57104 PCIe Endpoint **FPGA Network Interface Controller** IAP Controller SPI Flash Register **Bus Master** 1 î Sync I/O 32 x Sync I/O 🖨 Packet Handling Port 4 TSN Switch EEPROM < Control Register Switch Fabric **PPS Output** SGMII SGMII SGMII SGMII Gigabit Gigabit PHY PHY PHY PHY Port 1 Port 2 Port 3

### **Target Applications**

- Enable TSN on Industrial Automation Platforms

- Fieldbus over TSN Gateway

- Converge IT & OT Networks

## **ASIX Electronics Corporation**

4F, No. 8, Hsin Ann Road, Hsinchu Science Park, Hsinchu, 30078, Taiwan TEL: +886-3-5799500 FAX: +886-3-5799558

Email: sales@asix.com.tw https://www.asix.com.tw/