# M.2 (P42) 4TE3 Series

| Customer:          |  |

|--------------------|--|

| Customer           |  |

| Part<br>Number:    |  |

| Innodisk           |  |

| Part<br>Number:    |  |

| Innodisk           |  |

| <b>Model Name:</b> |  |

| Date:              |  |

|                    |  |

| Innodisk | Customer |

|----------|----------|

| Approver | Approver |

|          |          |

|          |          |

|          |          |

# Total Solution For Industrial Flash Storage

### **Features:**

- PCIe Gen.4 x4, NVMe SSD

- Innodisk 3D TLC NAND

- M.2 2242

- Standard temperature

- iPowerguard

- iDataguard

- Dynamic Thermal Management

- Hybrid Write Mode with SLC Cache Enable

- 256-bit AES hardware-based encryption

- Support Write Protection (Optional)

- Support TCG OPAL function (Optional)

# **Performance:**

- Sequential Read up to 3,550 MB/s

- Sequential Write up to 3,150 MB/s

# **Power Requirements:**

| Input Voltage:               | 3.3V± 5% |

|------------------------------|----------|

| Max Operating Wattage (R/W): | 4.8W     |

| Idle Wattage:                | 1.0W     |

# **Reliability:**

| Capacity | TBW  | DWPD |

|----------|------|------|

| 128GB    | 87   | 0.73 |

| 256GB    | 180  | 0.75 |

| 512GB    | 421  | 0.88 |

| 1TB      | 982  | 1.03 |

| 2TB      | 2078 | 1.09 |

| Data Retention | 10 Years |  |

|----------------|----------|--|

| Warranty       | 3 Years  |  |

For warranty details, please refer to:

https://www.innodisk.com/en/support\_and\_service/warranty

# **Table of contents**

| LIST OF FIGURES                             | 7  |

|---------------------------------------------|----|

| 1. PRODUCT OVERVIEW                         | 8  |

| 1.1 Introduction of Innodisk M.2 (P42) 4TE3 | 8  |

| 1.2 PRODUCT VIEW AND MODELS                 |    |

| 2. PRODUCT SPECIFICATIONS                   | 9  |

| 2.1 CAPACITY AND DEVICE PARAMETERS          | g  |

| 2.2 Performance                             |    |

| 2.3 ELECTRICAL SPECIFICATIONS               | 10 |

| 2.3.1 Power Requirement                     |    |

| 2.3.2 Power Consumption                     |    |

| 2.4 ENVIRONMENTAL SPECIFICATIONS            | 10 |

| 2.4.1 Temperature Ranges                    |    |

| 2.4.2 Humidity                              |    |

| 2.4.3 Shock and Vibration                   |    |

| 2.4.4 Mean Time between Failures (MTBF)     |    |

| 2.5 CE and FCC Compatibility                |    |

| 2.6 RoHS COMPLIANCE                         |    |

| 2.7 RELIABILITY                             | 12 |

| 2.8 Transfer Mode                           |    |

| 2.9 PIN ASSIGNMENT                          | 13 |

| 2.10 Mechanical Dimensions                  |    |

| 2.11 ASSEMBLY WEIGHT                        |    |

| 2.12 SEEK TIME                              |    |

| 2.13 NAND FLASH MEMORY                      | 14 |

| 3. THEORY OF OPERATION                      | 15 |

| 3.1 Overview                                |    |

| 3.2 PCIE GEN.4 x4 CONTROLLER                | 15 |

| 3.3 Error Detection and Correction          | 15 |

| 3.4 WEAR-LEVELING                           | 16 |

| 3.5 BAD BLOCKS MANAGEMENT                   | 16 |

| 3.6 GARBAGE COLLECTION/TRIM                 | 16 |

| 3.7 End to End Data Path Protection         | 16 |

| 3.8 THERMAL MANAGEMENT                      | 16 |

| 3.9 THERMAL THROTTLING                      | 17 |

| 3.10 iDataGuard                             | 17 |

| 3.11 TCG OPAL (OPTIONAL)                    | 17 |

| 4. INSTALLATION REQUIREMENTS                | 18 |

V1.1

|   | 4.1 M.2 (P42) 4TE3 PIN DIRECTIONS             | 18 |

|---|-----------------------------------------------|----|

|   | 4.2 ELECTRICAL CONNECTIONS FOR M.2 (P42) 4TE3 |    |

|   | 4.3 DEVICE DRIVE                              | 18 |

| 5 | . SMART / HEALTH INFORMATION                  | 19 |

|   | 5.1 GET LOG PAGE (LOG IDENTIFIER 02H)         | 19 |

|   | . PART NUMBER RULE                            |    |

| _ | · · · · · · · · · · · · · · · · · · ·         |    |

# **REVISION HISTORY**

| Revision | Description            | Date       |

|----------|------------------------|------------|

| V1.0     | First Release          | Nov., 2023 |

| V1.1     | Update Product Feature | Feb., 2024 |

# **List of Tables**

| TABLE 1: DEVICE PARAMETERS                              | 9  |

|---------------------------------------------------------|----|

| Table 2: Performance- 112 Layers 3D TLC                 | 9  |

| Table 3: Innodisk M.2 (P42) 4TE3 Power Requirement      | 10 |

| Table 4: Power Consumption                              | 10 |

| Table 5: Temperature range for M.2 (P42) 4TE3           | 10 |

| Table 6: Shock/Vibration Testing for M.2 (P42) 4TE3     | 10 |

| Table 7: M.2 (P42) 4TE3 MTBF                            | 11 |

| Table 8: M.2 (P42) 4TE3 ESD                             | 11 |

| Table 9: M.2 (P42) 4TE3 TBW                             | 12 |

| Table 10: Innodisk M.2 (P42) 4TE3 Pin Assignment        | 13 |

| Table 11: Get Log Page – SMART / Health Information Log | 19 |

# **List of Figures**

| FIGURE 1: INNODISK M.2 (P42) 4TE3 (STANDARD)    | 8  |

|-------------------------------------------------|----|

| FIGURE 2: INNODISK M.2 (P42) 4TE3 DIAGRAM       | 14 |

| FIGURE 3: INNODISK M.2 (P42) 4TE3 BLOCK DIAGRAM |    |

| FIGURE 4: SIGNAL SEGMENT AND POWER SEGMENT      |    |

# 1. Product Overview

# 1.1 Introduction of Innodisk M.2 (P42) 4TE3

Innodisk M.2 (P42) 4TE3 is a NVM Express DRAM-less SSD designed with PCIe interface and industrial 3D TLC NAND Flash. M.2 (P42) 4TE3 supports PCIe Gen.4 x4 and it is compliant with NVMe 1.4 providing excellent top and also sustained performance. With sophisticated error detection and correction (ECC) functions, the module can provide full End-to-end Data Path Protection that secures the data transmission between the host system and NAND Flash.

Innodisk M.2 (P42) 4TE3 is designed with AES engine, which is a built in controller. When controller receives the data package from host, AES engine encrypts the data package and saves the encrypted data into NAND flash. Thus, unauthorized personal has no access to decrypt the data in NAND flash.

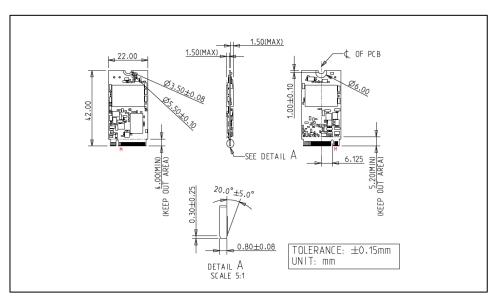

### 1.2 Product View and Models

Innodisk M.2 (P42) 4TE3 is available in follow capacities with industrial 3D TLC flash ICs.

M.2 (P42) 4TE3 128GB

M.2 (P42) 4TE3 256GB

M.2 (P42) 4TE3 512GB

M.2 (P42) 4TE3 1TB

M.2 (P42) 4TE3 2TB

Figure 1: Innodisk M.2 (P42) 4TE3 (Standard)

# 1.3 PCIe Interface

Innodisk M.2 (P42) 4TE3 supports PCIe Gen.4 interface and compliant with NVMe 1.4. M.2 (P42) 4TE3 can work under PCIe Gen. 1, Gen. 2 and Gen. 3.

Most of operating system includes NVMe in-box driver now. For more information about the driver support in each OS, please visit <a href="https://nvmexpress.org/drivers/">https://nvmexpress.org/drivers/</a>.

# 2. Product Specifications

# 2.1 Capacity and Device Parameters

M.2 (P42) 4TE3 device parameters are shown in Table 1.

**Table 1: Device parameters**

| Capacity | Cylinders | Heads | Sectors | LBA        | User<br>Capacity(MB) |

|----------|-----------|-------|---------|------------|----------------------|

| 128GB    | 16383     |       |         | 234441648  | 114473               |

| 256GB    |           |       |         | 468862128  | 228937               |

| 512GB    |           | 16    | 63      | 937703088  | 457863               |

| 1TB      |           |       |         | 1875385008 | 915715               |

| 2TB      |           |       |         | 3750748848 | 1831420              |

### 2.2 Performance

Burst Transfer Rate: 8 GB/s

Table 2: Performance- 112 Layers 3D TLC

| Capacity         | Unit | 128GB   | 256GB   | 512GB   | 1TB     | 2ТВ     |

|------------------|------|---------|---------|---------|---------|---------|

| Sequential*      |      | 1,450   | 2,900   | 2,900   | 3,550   | 3,300   |

| Read (Q8T1)      |      | 1,430   | 2,900   | 2,900   | 3,330   | 3,300   |

| Sequential*      |      | 800     | 1 550   | 1 500   | 2.050   | 2 150   |

| Write (Q8T1)     |      | 800     | 1,550   | 1,500   | 3,050   | 3,150   |

| Sustained        | MB/s |         |         |         |         |         |

| Sequential Read  |      | 710     | 1,400   | 1,300   | 1,900   | 1,750   |

| (Avg.)***        |      |         |         |         |         |         |

| Sustained        |      |         |         |         |         |         |

| Sequential Write |      | 170     | 250     | 210     | 420     | 430     |

| (Avg.)***        |      |         |         |         |         |         |

| 4KB Random**     |      | 4E 000  | 97.000  | 92.000  | 226 000 | 172 000 |

| Read (Q32T16)    | IOPS | 45,000  | 87,000  | 83,000  | 336,000 | 172,000 |

| 4KB Random**     |      | 105.000 | 271 000 | 272 000 | 627.000 | FF7 000 |

| Write (Q32T16)   |      | 195,000 | 371,000 | 373,000 | 637,000 | 557,000 |

Note: \* Performance results are 4TE3 with Innodisk BiCS5 NAND composition measured in Room Temperature with Out-of-Box devices and may vary depending on overall system setup. In addition, 4TE3 series adopt hybrid mode which enables SLC cache followed by TLC direct write to strike balance between burst performance and steady overall stability. Note: \*\* Performance results are based on CrystalDiskMark 8.0.1 with file size 1000MB. Unit of 4KB item is IOPS. Note: \*\*\* Performance results are based on AIDA 64 v5.98 with block size 1MB of Linear Read & Write Test Item.

# 2.3 Electrical Specifications

# 2.3.1 Power Requirement

Table 3: Innodisk M.2 (P42) 4TE3 Power Requirement

| Item          | Symbol   | Rating        | Unit     |

|---------------|----------|---------------|----------|

| Input voltage | $V_{IN}$ | +3.3 DC +- 5% | <b>V</b> |

# 2.3.2 Power Consumption

**Table 4: Power Consumption**

| Mode          | Power Consumption (W) |

|---------------|-----------------------|

| Read          | 4.8                   |

| Write         | 4.8                   |

| Idle          | 1.0                   |

| Power-on peak | 3.6                   |

Target: M.2 (P42) 4TE3 2TB

Note: Current results may vary depending on system components and power circuit design. Please refer to the test report for other capacities.

# 2.4 Environmental Specifications

# 2.4.1 Temperature Ranges

Table 5: Temperature range for M.2 (P42) 4TE3

| Temperature | Range                        |

|-------------|------------------------------|

| Operating   | Standard Grade: 0°C to +70°C |

| Storage     | -40°C to +85°C               |

# 2.4.2 Humidity

Relative Humidity: 10-95%, non-condensing

# 2.4.3 Shock and Vibration

Table 6: Shock/Vibration Testing for M.2 (P42) 4TE3

| Reliability Test Conditions |                                 | Reference Standards |

|-----------------------------|---------------------------------|---------------------|

| Vibration                   | 7 Hz to 2K Hz, 20G, 3 axes      | IEC 60068-2-6       |

| Mechanical Shock            | Duration: 0.5ms, 1500 G, 3 axes | IEC 60068-2-27      |

# 2.4.4 Mean Time between Failures (MTBF)

Table 7 summarizes the MTBF prediction results for various M.2 (P42) 4TE3 configurations. The analysis was performed using a RAM Commander<sup>™</sup> failure rate prediction.

- **Failure Rate**: The total number of failures within an item population, divided by the total number of life units expended by that population, during a particular measurement interval under stated condition.

- **Mean Time between Failures (MTBF)**: A basic measure of reliability for repairable items: The mean number of life units during which all parts of the item perform within their specified limits, during a particular measurement interval under stated conditions.

Table 7: M.2 (P42) 4TE3 MTBF

| Product Condition       |                           | MTBF (Hours) |

|-------------------------|---------------------------|--------------|

| Innodisk M.2 (P42) 4TE3 | Telcordia SR-332 GB, 25°C | >3,000,000   |

# 2.5 CE and FCC Compatibility

M.2 (P42) 4TE3 conforms to CE and FCC requirements.

Table 8: M.2 (P42) 4TE3 ESD

| Reliability                   | Reference standards |

|-------------------------------|---------------------|

| Electrostatic Discharge (ESD) | EC 61000-4-2 ESD    |

# 2.6 RoHS Compliance

M.2 (P42) 4TE3 is fully compliant with RoHS directive.

# 2.7 Reliability

Table 9: M.2 (P42) 4TE3 TBW

| Parameter       |       | Value                       |                               |

|-----------------|-------|-----------------------------|-------------------------------|

| Read Cycles     |       | Unlimited Read Cycles       |                               |

| Flash enduranc  | e     | 3,000 P/E cycles            |                               |

| Error Correct C | ode   | Support(LDPC)               |                               |

| Data Retention  |       | Under 40°C:                 |                               |

|                 |       | 10 Years at Initial NAND St | atus; 1 Year at NAND Life End |

| TBW* (Total By  | tes W | <b>ritten)</b> Unit: TB     |                               |

| Capacity        |       | Sequential workload         | Client workload               |

| 128GB           |       | 341                         | 87                            |

| 256GB           |       | 682                         | 180                           |

| 512GB           |       | 1364                        | 421                           |

| 1TB             |       | 2727                        | 982                           |

#### \* Note:

2TB

1. Sequential: Mainly sequential write are estimated by PassMark Burnin Test v8.1 pro.

5454

2. Client: Follow JESD218 Test method and JESD219A Workload, tested by ULINK. (The capacity lower than 64GB client workload is not specified in JEDEC219A, the values are estimated.)

2078

3. Based on out-of-box performance.

# 2.8 Transfer Mode

M.2 (P42) 4TE3 support following transfer mode:

PCIe Gen. 4: 2 GB/s

PCIe Gen. 3: 1 GB/s

PCIe Gen. 2: 500 MB/s

PCIe Gen. 1: 250 MB/s

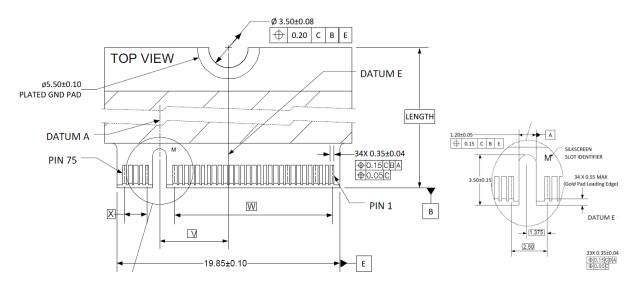

# 2.9 Pin Assignment

Innodisk M.2 (P42) 4TE3 follows standard M.2 spec, socket 3 key M PCIe-based SSD pinout. See Table 10 for M.2 (P42) 4TE3 pin assignment.

Table 10: Innodisk M.2 (P42) 4TE3 Pin Assignment

| Signal Name                | Pin # | Pin # | Signal Name |

|----------------------------|-------|-------|-------------|

| -                          |       | 75    | GND         |

| 3.3V                       | 74    | 73    | GND         |

| 3.3V                       | 72    | 71    | GND         |

| 3.3V                       | 70    | 69    | NC          |

| NC                         | 68    | 67    | NC          |

| Notch                      | 66    | 65    | Notch       |

| Notch                      | 64    | 63    | Notch       |

| Notch                      | 62    | 61    | Notch       |

| Notch                      | 60    | 59    | Notch       |

| NC                         | 58    | 57    | GND         |

| NC                         | 56    | 55    | REFCLKp     |

| NC                         | 54    | 53    | REFCLKn     |

| CLKREQ# (I/O)(0/3.3V)      | 52    | 51    | GND         |

| PERST# (I)(0/3.3V)         | 50    | 49    | PERp0       |

| NC                         | 48    | 47    | PERn0       |

| NC                         | 46    | 45    | GND         |

| NC (reserved for ALERT#)   | 44    | 43    | PETp0       |

| NC (reserved for SMB_DATA) | 42    | 41    | PETn0       |

| NC (reserved for SMB_CLK)  | 40    | 39    | GND         |

| NC                         | 38    | 37    | PERp1       |

| NC                         | 36    | 35    | PERn1       |

| NC                         | 34    | 33    | GND         |

| NC                         | 32    | 31    | PETp1       |

| NC                         | 30    | 29    | PETn1       |

| NC                         | 28    | 27    | GND         |

| NC                         | 26    | 25    | PERp2       |

| NC                         | 24    | 23    | PERn2       |

| NC                         | 22    | 21    | GND         |

| NC                         | 20    | 19    | PETp2       |

| 3.3V                       | 18    | 17    | PETn2       |

| 3.3V                       | 16    | 15    | GND         |

| 3.3V                       | 14    | 13    | PERp3       |

| 3.3V           | 12 | 11 | PERn3 |

|----------------|----|----|-------|

| LED1# (O) (OD) | 10 | 9  | GND   |

| NC             | 8  | 7  | PETp3 |

| NC             | 6  | 5  | PETn3 |

| 3.3V           | 4  | 3  | GND   |

| 3.3V           | 2  | 1  | GND   |

# 2.10 Mechanical Dimensions

### M.2 Type 2242

Figure 2: Innodisk M.2 (P42) 4TE3 diagram

# 2.11 Assembly Weight

An Innodisk M.2 (P42) 4TE3 within NAND flash ICs, 128GB's weight is 7 grams approximately.

# 2.12 Seek Time

Innodisk M.2 (P42) 4TE3 is not of magnetic rotating design. There is no seek or rotational latency.

# 2.13 NAND Flash Memory

Innodisk M.2 (P42) 4TE3 uses industrial 3D TLC NAND flash memory, which is non-volatility, high reliability and high speed memory storage.

# 3. Theory of Operation

#### 3.1 Overview

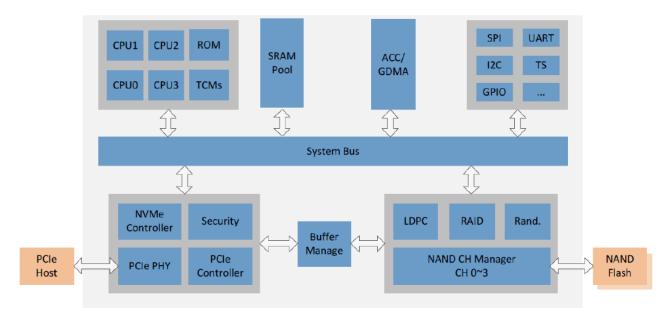

Figure 3 shows the operation of Innodisk M.2 (P42) 4TE3 from the system level, including the major hardware blocks.

Figure 3: Innodisk M.2 (P42) 4TE3 Block Diagram

Innodisk M.2 (P42) 4TE3 integrates a PCIe Gen.4 x4 controller and NAND flash memories. Communication with the host occurs through the host interface, using the standard NVM protocol. Communication with the flash device(s) occurs through the flash interface.

#### 3.2 PCIe Gen.4 x4 Controller

Innodisk M.2 (P42) 4TE3 is designed with innodisk ID309, a PCIe Gen.4 x4 controller which is compliant with NVMe 1.4, up to 64.0Gbps transfer speed. In addition, it is compliant with PCIe Gen. 1, Gen. 2 and Gen. 3 specification. The controller supports up to four channels for flash interface.

# 3.3 Error Detection and Correction

Innodisk M.2 (P42) 4TE3 is designed with hardware LDPC ECC engine with hard-decision and soft-decision decoding. Low-density parity-check (LDPC) codes have excellent error correcting performance close to the Shannon limit when decoded with the belief-propagation (BP) algorithm using soft-decision information.

# 3.4 Wear-Leveling

Flash memory can be erased with a limited number of cycles. This number is called the **erase cycle limit** or **write endurance limit** and is defined by the flash NAND vendor. The erase cycle limit applies to each individual erase block in the flash device.

Innodisk M.2 (P42) 4TE3 uses a combination of two types of wear leveling- dynamic and static wear leveling- to distribute write cycling across an SSD and balance erase count of each block, thereby extending device lifetime.

# 3.5 Bad Blocks Management

Bad Blocks are blocks that contain one or more invalid bits whose reliability are not guaranteed. The Bad Blocks may be presented while the SSD is shipped, or may develop during the lifetime of the SSD. When a Bad Block is detected, it will be flagged as unusable block by firmware. The SSD implement Bad Blocks management that consists of Bad Blocks replacement and Error Correcting to avoid data error occurred. The functions will be enabled automatically to transfer data from Bad Blocks to spare blocks, and correct error bit.

# 3.6 Garbage Collection/TRIM

Garbage collection and TRIM technology is used to maintain data consistency and perform continual data cleansing on SSDs. It runs as a background process, freeing up valuable controller resources while sorting good data into available blocks, and deleting bad blocks. It also significantly reduces write operations to the drive, thereby increasing the SSD's speed and lifespan.

#### 3.7 End to End Data Path Protection

End-to-end Data Path Protection that secures the data transmission between host system and NAND Flash. In the transmission path, no matter in or out, all buffer and storage implement Error Code Correction that optimizes the data integrity in the whole transmission of SSD.

# 3.8 Thermal Management

M.2 (P42) 4TE3 has built-in thermal sensor which can detect environment temperature of SSD. In the meantime, firmware will monitor the thermal sensor to prevent any failure of overheating. During extreme temperature, firmware will adjust the data transfer behavior to maintain the SSD's reliable operation.

# 3.9 Thermal throttling

Thermal throttling is a protective mechanism designed to safeguard components from potential damage caused by excessive temperatures. When an SSD approaches a critical temperature threshold, Innodisk firmware activates the thermal throttling mechanism to regulate the SSD's temperature. Thermal throttling is crucial for SSDs since it prevents drive damage, which could otherwise result in data loss. However, it's worth noting that when thermal throttling is activated, read and write tasks may experience a reduction in speed.

## 3.10 iDataGuard

Innodisk's iData Guard is a comprehensive data protection mechanism that functions before and after a sudden power outage to the SSD. Low-power detection terminates data writing before an abnormal power-off, while table-remapping after power-on deletes corrupt data and maintains data integrity. Innodisk's iData Guard provides effective power cycling management, preventing data stored in flash from degrading with use.

# 3.11 TCG OPAL (Optional)

OPAL is a set of specifications for features of data storage devices that enhance security. These specifications are published by the Trusted Computing Group's Storage Work Group. Innodisk 4TE3 is compliant with TCG OPAL 2.0(\*1). The capability of TCG OPAL Security mode allows multiple users with independent access control to read/write/erase independent data areas (LBA ranges). Each locking range adjusts by authenticated authority. Note that by default there is a single "Global Range" that encompasses the whole user data area. In TCG Opal Security Mode, Revert, Revert SP and GenKey command can erase all of data including global range and locking range; in the meantime generate the new encrypted key.

\*1. You need to install TCG OPAL software to implement OPAL function, which is supplied by TCG OPAL software developed company

# 4. Installation Requirements

# 4.1 M.2 (P42) 4TE3 Pin Directions

Figure 4: Signal Segment and Power Segment

# 4.2 Electrical Connections for M.2 (P42) 4TE3

M.2 interconnect is based on a 75 position Edge Card connector. The 75 position connector is intended to be keyed so as to distinguish between families of host interfaces and the various Sockets used in general Platforms. M.2 (P42) 4TE3 is compliant with M.2 Socket 3 key M.

### 4.3 Device Drive

M.2 (P42) 4TE3 is compliant with NVMe 1.4. Both Operation System and BIOS should include NVMe driver to compatible with NVMe device. Nowadays, most of OS includes NVMe in-box driver now. For more information about the driver support in each OS, please visit the website <a href="https://nvmexpress.org/drivers/">https://nvmexpress.org/drivers/</a>. For BIOS NVMe driver support please contact with motherboard manufacturers.

# 5. SMART / Health Information

This log page is used to provide SMART and general health information. The information provided is over the life of the controller and is retained across power cycles. More details about Set Features command; please refer to NVM Express 1.4

# 5.1 Get Log Page (Log Identifier 02h)

Innodisk 4TE3 series SMART / Health Information Log are listed in following table.

Table 11: Get Log Page - SMART / Health Information Log

| ytes | Description                                                                                        |                                                                                      |  |  |  |  |

|------|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|--|--|--|

|      | Critical Warning: This field indicates critical warnings for the state of the controller. Ea       |                                                                                      |  |  |  |  |

|      | corresponds to a critical warning type; multiple bits may be set to `1'. If a bit is cleared to `0 |                                                                                      |  |  |  |  |

|      | then that cr                                                                                       | ritical warning does not apply. Critical warnings may result in an asynchronous even |  |  |  |  |

|      | notification                                                                                       | to the host. Bits in this field represent the state at the time the Get Log Page     |  |  |  |  |

|      | command is                                                                                         | s processed and may not reflect the state at the time a related asynchronous even    |  |  |  |  |

|      | notification                                                                                       | , if any, occurs or occurred.                                                        |  |  |  |  |

|      | Bit                                                                                                | Definition                                                                           |  |  |  |  |

|      | 0                                                                                                  | If set to '1', then the available spare capacity has fallen below the                |  |  |  |  |

|      |                                                                                                    | threshold.                                                                           |  |  |  |  |

|      | 1                                                                                                  | If set to `1', then a temperature is:                                                |  |  |  |  |

| _    |                                                                                                    | a) greater than or equal to an over temperature threshold.                           |  |  |  |  |

| 0    |                                                                                                    | b) less than or equal to an under temperature threshold.                             |  |  |  |  |

|      | 2                                                                                                  | If set to `1', then the NVM subsystem reliability has been degraded due to           |  |  |  |  |

|      |                                                                                                    | significant media related errors or any internal error that degrades NVM             |  |  |  |  |

|      |                                                                                                    | subsystem reliability.                                                               |  |  |  |  |

|      | 3                                                                                                  | If set to `1', then all of the media has been placed in read only mode. The          |  |  |  |  |

|      |                                                                                                    | controller shall not set this bit to '1' if the read-only condition on the media     |  |  |  |  |

|      |                                                                                                    | is a result of a change in the write protection state of a namespace.                |  |  |  |  |

|      | 4                                                                                                  | If set to `1', then the volatile memory backup device has failed. This field is      |  |  |  |  |

|      |                                                                                                    | only valid if the controller has a volatile memory backup solution.                  |  |  |  |  |

|      | 5                                                                                                  | If set to `1', then the Persistent Memory Region has become read-only or             |  |  |  |  |

|      |                                                                                                    | unreliable.                                                                          |  |  |  |  |

|      | 7:6                                                                                                | Reserved                                                                             |  |  |  |  |

|      |                                                                                                    |                                                                                      |  |  |  |  |

|     | Composite Temperature: Contains a value corresponding to a temperature in degrees Kelvin      |                                                                                                                                                |  |  |  |

|-----|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|     | that represents the current composite temperature of the controller and namespace(s)          |                                                                                                                                                |  |  |  |

|     | associated with that controller. The manner in which this value is computed is implementation |                                                                                                                                                |  |  |  |

| 1:2 | specific and                                                                                  | may not represent the actual temperature of any physical point in the NVM                                                                      |  |  |  |

|     | subsystem. T                                                                                  | he value of this field may be used to trigger an asynchronous event.                                                                           |  |  |  |

|     | Warning and                                                                                   | critical overheating composite temperature threshold values are reported by the                                                                |  |  |  |

|     | WCTEMP and                                                                                    | CCTEMP fields in the Identify Controller data structure.                                                                                       |  |  |  |

|     | Available Spare: Contains a normalized percentage (0 to 100%) of the remaining spare          |                                                                                                                                                |  |  |  |

| 3   | capacity available.                                                                           |                                                                                                                                                |  |  |  |

|     | Available Spare Threshold: When the Available Spare falls below the threshold indicated in    |                                                                                                                                                |  |  |  |

| 4   | this field, an a                                                                              | asynchronous event completion may occur. The value is indicated as a normalized                                                                |  |  |  |

|     | percentage (0                                                                                 | to 100%). The values 101 to 255 are reserved.                                                                                                  |  |  |  |

|     | Percentage l                                                                                  | <b>Used:</b> Contains a vendor specific estimate of the percentage of NVM subsystem life                                                       |  |  |  |

|     | used based or                                                                                 | n the actual usage and the manufacturer's prediction of NVM life. A value of 100                                                               |  |  |  |

|     | indicates that                                                                                | the estimated endurance of the NVM in the NVM subsystem has been consumed,                                                                     |  |  |  |

| 5   | but may not ir                                                                                | ndicate an NVM subsystem failure. The value is allowed to exceed 100. Percentages                                                              |  |  |  |

| 5   | greater than 2                                                                                | 254 shall be represented as 255. This value shall be updated once per power-on                                                                 |  |  |  |

|     | hour (when the controller is not in a sleep state).                                           |                                                                                                                                                |  |  |  |

|     | Refer to the                                                                                  | JEDEC JESD218A standard for SSD device life and endurance measurement                                                                          |  |  |  |

|     | techniques.                                                                                   |                                                                                                                                                |  |  |  |

|     | Endurance G                                                                                   | Group Critical Warning Summary: This field indicates critical warnings for the                                                                 |  |  |  |

|     |                                                                                               | rance Groups. Each bit corresponds to a critical warning type, multiple bits may be                                                            |  |  |  |

|     |                                                                                               | bit is cleared to '0', then that critical warning does not apply to any Endurance                                                              |  |  |  |

|     |                                                                                               | I warnings may result in an asynchronous event notification to the host. Bits in this                                                          |  |  |  |

|     |                                                                                               | t the current associated state and are not persistent.                                                                                         |  |  |  |

|     | If a bit is set t                                                                             | to `1' in one or more Endurance Groups, then the corresponding bit shall be set to                                                             |  |  |  |

|     | `1' in this field                                                                             |                                                                                                                                                |  |  |  |

|     |                                                                                               |                                                                                                                                                |  |  |  |

|     | Bit                                                                                           | Definition                                                                                                                                     |  |  |  |

| 6   | 0                                                                                             | If set to `1', then the available spare capacity of one or more Endurance                                                                      |  |  |  |

|     |                                                                                               | Groups has fallen below the threshold.                                                                                                         |  |  |  |

|     | 1                                                                                             | Reserved                                                                                                                                       |  |  |  |

|     | 2                                                                                             | If set to `1', then the reliability of one or more Endurance Groups has been                                                                   |  |  |  |

|     |                                                                                               | degraded due to significant media related errors or any internal error that                                                                    |  |  |  |

|     |                                                                                               | degrades NVM subsystem reliability.                                                                                                            |  |  |  |

|     |                                                                                               | acgrades itti subsystem remasmey.                                                                                                              |  |  |  |

|     | 3                                                                                             | If set to `1', then the namespaces in one or more Endurance Groups have                                                                        |  |  |  |

|     | 3                                                                                             |                                                                                                                                                |  |  |  |

|     | 3                                                                                             | If set to `1', then the namespaces in one or more Endurance Groups have                                                                        |  |  |  |

|     | 7:4                                                                                           | If set to '1', then the namespaces in one or more Endurance Groups have been placed in read only mode not as a result of a change in the write |  |  |  |

| 7:31    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32:47   | <b>Data Units Read:</b> Contains the number of 512 byte data units the host has read from the controller as part of processing a SMART Data Units Read Command; this value does not include metadata. This value is reported in thousands (i.e., a value of 1 corresponds to 1,000 units of 512 bytes read) and is rounded up (e.g., one indicates that the number of 512 byte data units read is from 1 to 1,000, three indicates that the number of 512 byte data units read is from                                                                                                                                                                                                                                  |

| 32.47   | 2,001 to 3,000).  Refer to the specific I/O Command Set specification for the list of SMART Data Units Read Commands that affect this field.  A value of 0h in this field indicates that the number of SMART Data Units Read is not reported.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 48:63   | Data Units Written: Contains the number of 512 byte data units the host has written to the controller as part of processing a User Data Out Command; this value does not include metadata. This value is reported in thousands (i.e., a value of 1 corresponds to 1,000 units of 512 bytes written) and is rounded up (e.g., one indicates that the number of 512 byte data units written is from 1 to 1,000, three indicates that the number of 512 byte data units written is from 2,001 to 3,000).  Refer to the specific I/O Command Set specification for the list of User Data Out Commands that affect this field.  A value of 0h in this field indicates that the number of Data Units Written is not reported. |

| 64:79   | Host Read Commands: Contains the number of SMART Host Read Commands completed by the controller.  Refer to the specific I/O Command Set specification for the list of SMART Host Read Commands that affect this field.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 80:95   | Host Write Commands: Contains the number of User Data Out Commands completed by the controller.  Refer to the specific I/O Command Set specification for the list of User Data Out Commands that affect this field.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 96:111  | Controller Busy Time: Contains the amount of time the controller is busy with I/O commands. The controller is busy when there is a command outstanding to an I/O Queue (specifically, a command was issued via an I/O Submission Queue Tail doorbell write and the corresponding completion queue entry has not been posted yet to the associated I/O Completion Queue). This value is reported in minutes.                                                                                                                                                                                                                                                                                                             |

| 112:127 | Power Cycles: Contains the number of power cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 128:143 | <b>Power On Hours:</b> Contains the number of power-on hours. This may not include time that the controller was powered and in a non-operational power state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 144:159 | <b>Unsafe Shutdowns:</b> Contains the number of unsafe shutdowns. This count is incremented when the controller does not report it is safe to power down prior to loss of main power.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 160:175 | Media and Data Integrity Errors: Contains the number of occurrences where the controller          |  |  |  |  |  |  |  |  |  |  |

|---------|---------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

|         | detected an unrecovered data integrity error. Errors such as uncorrectable ECC, CRC checksum      |  |  |  |  |  |  |  |  |  |  |

|         | failure, or LBA tag mismatch are included in this field. Errors introduced as a result of a Write |  |  |  |  |  |  |  |  |  |  |

|         | Uncorrectable command (refer to the NVM Command Set Specification) may or may not be              |  |  |  |  |  |  |  |  |  |  |

|         | included in this field.                                                                           |  |  |  |  |  |  |  |  |  |  |

| 176:191 | Number of Error Information Log Entries: Contains the number of Error Information log             |  |  |  |  |  |  |  |  |  |  |

|         | entries over the life of the controller.                                                          |  |  |  |  |  |  |  |  |  |  |

|         | Warning Composite Temperature Time: Contains the amount of time in minutes that the               |  |  |  |  |  |  |  |  |  |  |

|         | controller is operational and the Composite Temperature is greater than or equal to the Warning   |  |  |  |  |  |  |  |  |  |  |

| 192:195 | Composite Temperature Threshold (WCTEMP) field and less than the Critical Composite               |  |  |  |  |  |  |  |  |  |  |

| 192:195 | Temperature Threshold (CCTEMP) field in the Identify Controller data structure in Figure 275.     |  |  |  |  |  |  |  |  |  |  |

|         | If the value of the WCTEMP or CCTEMP field is 0h, then this field is always cleared to 0h         |  |  |  |  |  |  |  |  |  |  |

|         | regardless of the Composite Temperature value.                                                    |  |  |  |  |  |  |  |  |  |  |

|         | Critical Composite Temperature Time: Contains the amount of time in minutes that the              |  |  |  |  |  |  |  |  |  |  |

|         | controller is operational and the Composite Temperature is greater than or equal to the Critical  |  |  |  |  |  |  |  |  |  |  |

| 196:199 | Composite Temperature Threshold (CCTEMP) field in the Identify Controller data structure.         |  |  |  |  |  |  |  |  |  |  |

|         | If the value of the CCTEMP field is 0h, then this field is always cleared to 0h regardless of the |  |  |  |  |  |  |  |  |  |  |

|         | Composite Temperature value.                                                                      |  |  |  |  |  |  |  |  |  |  |

| 200:201 | <b>Temperature Sensor 1:</b> Contains the current temperature reported by the embedded thermal    |  |  |  |  |  |  |  |  |  |  |

| 200.201 | sensor in the controller.                                                                         |  |  |  |  |  |  |  |  |  |  |

| 202:203 | <b>Temperature Sensor 2:</b> Contains the current temperature reported by the embedded thermal    |  |  |  |  |  |  |  |  |  |  |

| 202.203 | sensor in the NAND Flash (Channel #0 and CE #0).                                                  |  |  |  |  |  |  |  |  |  |  |

| 204:205 | <b>Temperature Sensor 3:</b> Contains the current temperature reported by the embedded thermal    |  |  |  |  |  |  |  |  |  |  |

| 2011203 | sensor in the NAND Flash (Channel #0 and CE #0).                                                  |  |  |  |  |  |  |  |  |  |  |

| 206:207 | <b>Temperature Sensor 4:</b> Contains the current temperature reported by the embedded thermal    |  |  |  |  |  |  |  |  |  |  |

|         | sensor in the NAND Flash (Last channel and CE #0).                                                |  |  |  |  |  |  |  |  |  |  |

| 208:209 | <b>Temperature Sensor 5:</b> Contains the current temperature reported by temperature sensor 5.   |  |  |  |  |  |  |  |  |  |  |

| 210:211 | <b>Temperature Sensor 6:</b> Contains the current temperature reported by temperature sensor 6.   |  |  |  |  |  |  |  |  |  |  |

| 212:213 | <b>Temperature Sensor 7:</b> Contains the current temperature reported by temperature sensor 7.   |  |  |  |  |  |  |  |  |  |  |

| 214:215 | <b>Temperature Sensor 8:</b> Contains the current temperature reported by temperature sensor 8.   |  |  |  |  |  |  |  |  |  |  |

|         | Thermal Management Temperature 1 Transition Count: Contains the number of times the               |  |  |  |  |  |  |  |  |  |  |

| 216:219 | controller transitioned to lower power active power states or performed vendor specific thermal   |  |  |  |  |  |  |  |  |  |  |

|         | management actions while minimizing the impact on performance in order to attempt to reduce       |  |  |  |  |  |  |  |  |  |  |

|         | the Composite Temperature because of the host controlled thermal management feature.              |  |  |  |  |  |  |  |  |  |  |

|         | Thermal Management Temperature 2 Transition Count: Contains the number of times the               |  |  |  |  |  |  |  |  |  |  |

|         | controller transitioned to lower power active power states or performed vendor specific thermal   |  |  |  |  |  |  |  |  |  |  |

| 220:223 | management actions regardless of the impact on performance (e.g., heavy throttling) in order      |  |  |  |  |  |  |  |  |  |  |

|         |                                                                                                   |  |  |  |  |  |  |  |  |  |  |

|         | to attempt to reduce the Composite Temperature because of the host controlled thermal             |  |  |  |  |  |  |  |  |  |  |

|         | <b>Total Time For Thermal Management Temperature 1:</b> Contains the number of seconds that     |  |  |  |  |  |  |  |  |  |  |

|---------|-------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

|         | the controller had transitioned to lower power active power states or performed vendor specific |  |  |  |  |  |  |  |  |  |  |

| 224:227 | thermal management actions while minimizing the impact on performance in order to attempt to    |  |  |  |  |  |  |  |  |  |  |

|         | reduce the Composite Temperature because of the host controlled thermal management              |  |  |  |  |  |  |  |  |  |  |

|         | feature.                                                                                        |  |  |  |  |  |  |  |  |  |  |

|         | <b>Total Time For Thermal Management Temperature 2:</b> Contains the number of seconds that     |  |  |  |  |  |  |  |  |  |  |

| 228:231 | the controller had transitioned to lower power active power states or performed vendor specific |  |  |  |  |  |  |  |  |  |  |

|         | thermal management actions regardless of the impact on performance (e.g., heavy throttling)     |  |  |  |  |  |  |  |  |  |  |

|         | in order to attempt to reduce the Composite Temperature because of the host controlled thermal  |  |  |  |  |  |  |  |  |  |  |

|         | management feature.                                                                             |  |  |  |  |  |  |  |  |  |  |

| 232:337 | Reserved                                                                                        |  |  |  |  |  |  |  |  |  |  |

| 338:345 | Later Bad Count                                                                                 |  |  |  |  |  |  |  |  |  |  |

| 346:353 | Power-On hours Count                                                                            |  |  |  |  |  |  |  |  |  |  |

| 354:361 | Drive Power Cycle Count                                                                         |  |  |  |  |  |  |  |  |  |  |

| 362:369 | Total Bad Block Count                                                                           |  |  |  |  |  |  |  |  |  |  |

| 370:377 | User Max Erase Count                                                                            |  |  |  |  |  |  |  |  |  |  |

| 378:385 | User Avg Erase Count                                                                            |  |  |  |  |  |  |  |  |  |  |

| 386:393 | Device Life                                                                                     |  |  |  |  |  |  |  |  |  |  |

| 394:401 | Spare Block Count                                                                               |  |  |  |  |  |  |  |  |  |  |

| 402:409 | Program Fail Count                                                                              |  |  |  |  |  |  |  |  |  |  |

| 410:417 | Erase Fail Count                                                                                |  |  |  |  |  |  |  |  |  |  |

| 418:425 | Unexpected Power Loss Count                                                                     |  |  |  |  |  |  |  |  |  |  |

| 426:433 | Temperature ( Kelvin - K °K)                                                                    |  |  |  |  |  |  |  |  |  |  |

| 434:441 | Flash ID                                                                                        |  |  |  |  |  |  |  |  |  |  |

| 442:449 | Later Bad Block Info (Read / Write / Erase)                                                     |  |  |  |  |  |  |  |  |  |  |

| 450:457 | Total LBAs Written (unit = 32MB)                                                                |  |  |  |  |  |  |  |  |  |  |

| 458:465 | Total LBAs Read (unit = 32MB)                                                                   |  |  |  |  |  |  |  |  |  |  |

# 6. Part Number Rule

|                                                      | 1                                                   | 2     | 3                 | 4                | 5     | 6    | 7   | 8 | 9 | 10                                                       | 11                                                 | 12    | 13    | 14              | 15               | 16    | 17   | 18     | 19  | 20 | 21 |  |  |

|------------------------------------------------------|-----------------------------------------------------|-------|-------------------|------------------|-------|------|-----|---|---|----------------------------------------------------------|----------------------------------------------------|-------|-------|-----------------|------------------|-------|------|--------|-----|----|----|--|--|

| CODE                                                 | D                                                   | E     | М                 | 2                | 4     | -    | Α   | 2 | 8 | D                                                        | Н                                                  | 1     | K     | С               | A                | D     | L    | (W)    | -   | X  | X  |  |  |

|                                                      | finit                                               | tion  |                   |                  |       |      |     |   |   |                                                          |                                                    |       |       |                 |                  |       |      |        |     |    |    |  |  |

| Code 1 <sup>st</sup> (Disk)                          |                                                     |       |                   |                  |       |      |     |   |   |                                                          |                                                    | Cod   | e 14  | th (O           | pera             | ation | Ten  | npera  | tur | e) |    |  |  |

| . ,                                                  |                                                     |       |                   |                  |       |      |     |   |   |                                                          | C: Standard Grade ( $0^{\circ}$ ~ +70 $^{\circ}$ ) |       |       |                 |                  |       |      |        |     |    |    |  |  |

|                                                      |                                                     |       |                   |                  |       |      |     |   |   |                                                          |                                                    |       |       |                 |                  |       |      |        |     |    |    |  |  |

| Code 2 <sup>nd</sup> (Feature set)                   |                                                     |       |                   |                  |       |      |     |   |   |                                                          |                                                    |       | Code  | 15 <sup>t</sup> | <sup>h</sup> (Ir | nterr | al c | ontrol | )   |    |    |  |  |

| E : Embedded series                                  |                                                     |       |                   |                  |       |      |     |   |   | A٠                                                       | √Z: E                                              | BGA I | РСВ \ | /ersio          | on.              |       |      |        |     |    |    |  |  |

|                                                      |                                                     |       |                   |                  |       |      |     |   |   |                                                          |                                                    |       |       |                 |                  |       |      |        |     |    |    |  |  |

|                                                      | Code 3 <sup>rd</sup> ~5 <sup>th</sup> (Form factor) |       |                   |                  |       |      |     |   |   |                                                          | Code 16th (Channel of data transfer)               |       |       |                 |                  |       |      |        |     |    |    |  |  |

| M24: M.                                              | 2 Typ                                               | oe 22 | 242               |                  |       |      |     |   |   | D                                                        | D: Dual Channels                                   |       |       |                 |                  |       |      |        |     |    |    |  |  |

|                                                      |                                                     |       |                   |                  |       |      |     |   |   | Q                                                        | Q: Quad Channels                                   |       |       |                 |                  |       |      |        |     |    |    |  |  |

|                                                      |                                                     |       |                   |                  |       |      |     |   |   |                                                          |                                                    |       |       |                 |                  |       |      |        |     |    |    |  |  |

|                                                      |                                                     | Code  | e 7 <sup>th</sup> | ~9 <sup>th</sup> | ¹ (Ca | paci | ty) |   |   |                                                          | Code 17 <sup>th</sup> (Flash Type)                 |       |       |                 |                  |       |      |        |     |    |    |  |  |

| A28: 12                                              |                                                     |       |                   |                  |       |      |     |   |   | L/                                                       | L/Q: Innodisk 3D TLC                               |       |       |                 |                  |       |      |        |     |    |    |  |  |

| B56: 25                                              |                                                     |       |                   |                  |       |      |     |   |   |                                                          |                                                    |       |       |                 |                  |       |      |        |     |    |    |  |  |

| C12: 512GB                                           |                                                     |       |                   |                  |       |      |     |   |   |                                                          |                                                    |       |       |                 |                  |       |      |        |     |    |    |  |  |

| 01T: 1TB<br>02T: 2TB                                 |                                                     |       |                   |                  |       |      |     |   |   |                                                          |                                                    |       |       |                 |                  |       |      |        |     |    |    |  |  |

| 021. 211                                             | <u> </u>                                            |       |                   |                  |       |      |     |   |   |                                                          |                                                    |       |       |                 |                  |       |      |        |     |    |    |  |  |

| Code 10 <sup>th</sup> ~12 <sup>th</sup> (Controller) |                                                     |       |                   |                  |       |      |     |   |   |                                                          | Code 18 <sup>th</sup> (Optional Function)          |       |       |                 |                  |       |      |        |     |    |    |  |  |

| DH1: PCIe 4TE3 series                                |                                                     |       |                   |                  |       |      |     |   | W | W: H/W Write Protect Function                            |                                                    |       |       |                 |                  |       |      |        |     |    |    |  |  |

| DH2: PCIe 4TE3 series with TCG OPAL function         |                                                     |       |                   |                  |       |      |     |   |   |                                                          |                                                    |       |       |                 |                  |       |      |        |     |    |    |  |  |

| Code 13 <sup>th</sup> (Flash mode)                   |                                                     |       |                   |                  |       |      |     |   |   | Code 20 <sup>th</sup> ~21 <sup>st</sup> (Customize code) |                                                    |       |       |                 |                  |       |      |        |     |    |    |  |  |

| K: 112 Layers 3D TLC                                 |                                                     |       |                   |                  |       |      |     |   |   |                                                          |                                                    |       |       |                 |                  |       |      |        |     |    |    |  |  |

|                                                      |                                                     |       |                   |                  |       |      |     |   |   |                                                          |                                                    |       |       |                 |                  |       |      |        |     |    |    |  |  |

|                                                      |                                                     |       |                   |                  |       |      |     |   |   |                                                          |                                                    |       |       |                 |                  |       |      |        | _   |    |    |  |  |

|                                                      |                                                     |       |                   |                  |       |      |     |   |   |                                                          |                                                    |       |       |                 |                  |       |      |        |     |    |    |  |  |