## MS-9892

## (v1.x) Industrial Computer Board

## **Copyright and Trademarks Notice**

Copyright © Micro-Star Int'l Co., Ltd. All rights reserved. The MSI logo used is a registered trademark of Micro-Star Int'l Co., Ltd. All other marks and names mentioned may be trademarks of their respective owners. No warranty as to accuracy or completeness is expressed or implied. MSI reserves the right to make changes to this document without prior notice.

## **Revision History**

Revision Date V1.2 2020/09

## **Technical Support**

If a problem arises with your product and no solution can be obtained from the user's manual, please contact your place of purchase or local distributor. Alternatively, please visit https://www.msi.com/support/ for further guidance.

## **Safety Instructions**

- Always read the safety instructions carefully.

- Keep this User's Manual for future reference.

- Keep this equipment away from humidity.

- Lay this equipment on a reliable flat surface before setting it up.

- The openings on the enclosure are for air convection hence protects the equipment from overheating. DO NOT COVER THE OPENINGS.

- Make sure the voltage of the power source and adjust properly 110/220V before connecting the equipment to the power inlet.

- Place the power cord such a way that people can not step on it. Do not place anything over the power cord.

- Always Unplug the Power Cord before inserting any add-on card or module.

- All cautions and warnings on the equipment should be noted.

- Never pour any liquid into the opening that could damage or cause electrical shock.

- If any of the following situations arises, get the equipment checked by service personnel:

- ► The power cord or plug is damaged.

- Liquid has penetrated into the equipment.

- ▶ The equipment has been exposed to moisture.

- The equipment does not work well or you can not get it work according to User's Manual.

- The equipment has dropped and damaged.

- ► The equipment has obvious sign of breakage.

- DO NOT LEAVE THIS EQUIPMENT IN AN ENVIRONMENT UNCONDITIONED, STORAGE TEMPERATURE ABOVE 60°C, IT MAY DAMAGE THE FOUIPMENT

#### **Chemical Substances Information**

In compliance with chemical substances regulations, such as the EU REACH Regulation (Regulation EC No. 1907/2006 of the European Parliament and the Council), MSI provides the information of chemical substances in products at:

https://www.msi.com/html/popup/csr/evmtprtt\_pcm.html

## **Battery Information**

European Union:

Batteries, battery packs, and accumulators should not be disposed of as unsorted household waste. Please use the public collection system to return, recycle, or treat them in compliance with the local regulations.

Taiwan:

For better environmental protection, waste batteries should be collected separately for recycling or special disposal.

California. USA:

The button cell battery may contain perchlorate material and requires special handling when recycled or disposed of in California.

For further information please visit:

https://www.dtsc.ca.gov/hazardouswaste/perchlorate/

Danger of explosion if battery is incorrectly replaced. Replace only with the same or equivalent type recommended by the manufacturer.

## **CE Conformity**

Hereby, Micro-Star International CO., LTD declares that this device is in compliance with the essential safety requirements and other relevant provisions set out in the European Directive.

### FCC-B Radio Frequency Interference Statement

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the measures listed below:

- Reorient or relocate the receiving antenna.

- Increase the separation between the equipment and receiver.

- Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

- Consult the dealer or an experienced radio/television technician for help.

#### Notice 1

The changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to operate the equipment.

#### Notice 2

Shielded interface cables and AC power cord, if any, must be used in order to comply with the emission limits.

This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions:

- 1) this device may not cause harmful interference, and

- this device must accept any interference received, including interference that may cause undesired operation.

#### **WEEE Statement**

Under the European Union ("EU") Directive on Waste Electrical and Electronic Equipment, Directive 2012/19/EU, products of "electrical and electronic equipment" cannot be discarded as municipal waste anymore and manufacturers of covered electronic equipment will be obligated to take back such products at the end of their useful life.

## **CONTENTS**

|    | Copyright and Trademarks Notice              | ii   |

|----|----------------------------------------------|------|

|    | Revision History                             | ii   |

|    | Technical Support                            | ii   |

|    | Safety Instructions                          | iii  |

|    | Chemical Substances Information              | iv   |

|    | Battery Information                          | iv   |

|    | CE Conformity                                | V    |

|    | FCC-B Radio Frequency Interference Statement | V    |

|    | WEEE Statement                               | V    |

| 1  | Overview                                     | 1-1  |

|    | Motherboard Specifications                   | 1-2  |

|    | Motherboard Layout                           | 1-5  |

| 2  | Hardware Setup                               | 2-1  |

|    | Memory                                       |      |

|    | Power Supply                                 |      |

|    | Rear Panel I/O                               |      |

|    | Connector                                    |      |

|    | Jumper                                       | 2-14 |

|    | Slot                                         | 2-16 |

| 3  | BIOS Setup                                   | 3-1  |

|    | Entering Setup                               |      |

|    | The Menu Bar                                 |      |

|    | Main                                         |      |

|    | Advanced                                     | 3-6  |

|    | Boot                                         | 3-12 |

|    | Security                                     | 3-13 |

|    | Chipset                                      | 3-18 |

|    | Power                                        | 3-19 |

|    | Save & Exit                                  | 3-21 |

| Αŗ | ppendix GPIO WDT BKL Programming             | A-1  |

|    | Abstract                                     | A-2  |

|    | General Purposed IO                          |      |

|    | Watchdog Timer                               |      |

|    | LVDS Backlight Brightness Control            |      |

|    | SMBus Access                                 | A-7  |

## 1 Overview

Thank you for choosing the MS-9892, an excellent industrial computer board.

Based on the innovative Intel® Apollo Lake processor for optimal system efficiency, the MS-9892 accommodates versatile I/O interfaces and supports up to 2 DDR3L 1867MHz SO-DIMM slots to provide the maximum of 8GB memory capacity.

Designed to withstand harsh industrial conditions, the MS-9892 is engineered to provide reliable performance for a wide variety of industrial applications.

## **Motherboard Specifications**

#### **Processor**

- Intel® Atom™ X7-E3950 QC 1.6/2.0GHz (Burst)

- Intel® Atom™ X5-E3940 QC 1.6/1.8GHz (Burst)

- Intel® Atom™ X5-E3930 DC 1.3/1.8GHz (Burst)

- Intel® Pentium® N4200 QC 1.1/2.5GHz (Burst)

- Intel® Celeron® N3350 DC 1.1/2.4GHz (Burst)

- Intel® Celeron® J3455 QC 1.5/2.3GHz (Burst)

#### Memory

- 2 x SO-DIMM slots

- Dual-channel Non-ECC DDR3L, up to 1867MHz

- Up to 8GB

#### Network

- 2 x Intel® I210-IT GbE LAN (for Apollo Lake-I only)

- 2 x Intel® I211-AT GbE LAN (for Apollo Lake only)

#### **Storage**

■ 2 x SATA 6Gb/s ports (SATA2 shared with mSATA)

#### **Expansion Slot**

- 1 x PCle x1 slot

- 2 x Mini PCle slots

- » MINI PCIE1: full/half size, with SIM holder

- » MINI\_PCIE2: mSATA only, shared with SATA2

#### Internal I/O

- 1 x 4-pin power connector

- 1 x SATA power box header

- 1 x System fan header

- 3 x USB 2.0 box headers (6 ports)

- 2 x RS232/422/485 COM port box headers

- 4 x RS232 COM port box headers

- 2 x GPIO box headers

- 1 x Front panel header

- 1 x Front audio header

- 1 x S/PDIF header

- 1 x Audio amplifier box header

- 1 x SMBus box header

- 1 x Keyboard/mouse box header

- 1 x TPM header

- 1 x LVDS connector

- 1 x LVDS blacklight header & power jumper

- 1 x eDP connector

- 1 x Chassis intrusion header

- 1 x Clear CMOS jumper

- 1 x AT/ATX iumper

- 1 x eDP power jumper

- 1 x TXE F/W jumper

#### Rear I/O

- 1 x DC-In jack

- 4 x USB 3.2 Gen 1 ports

- 1 x HDMI port (co-lay DisplayPort by request)

- 1 x DisplayPort (co-lay HDMI port by request)

- 2 x RJ45 GbE LAN ports

- 1 x Line-Out jack

#### **Graphics**

- HD Graphics integrated in Intel® processor

- LVDS up to 1920 x 1200 @ 60 Hz

- HDMI up to 3840 x 2160 @ 30 Hz

- DisplayPort up to 4096 x 2160 @ 60 Hz

- eDP up to 3840 x 2160 @ 60 Hz

- Supports three independent displays: LVDS/HDMI/DisplayPort/eDP

#### **Audio**

- Realtek® ALC887/888S HD Audio Codec

- 1 x Audio amplifier box header

- 1 x S/PDIF header

- 1 x Line-Out jack

#### **Power**

- DC 12~24V

- 1 x 4-pin power connector

- 1 x DC-In jack

#### **Environment**

- Operating temperature: -10 ~ 60°C (for Apollo Lake)

- Operating temperature: -40 ~ 85°C (for Apollo Lake-I)

- Storage temperature: -20 ~ 80°C (for Apollo Lake)

- Storage temperature: -40 ~ 85°C (for Apollo Lake-I)

- Humidity: 10 ~ 90% RH, non-condensing

#### **Form Factor**

■ Mini-ITX: 170 mm x 170 mm

#### Certification

- EMC: CE, FCC, RCM, VCCI, BSMI /ClassB

- Safety: CB, UL

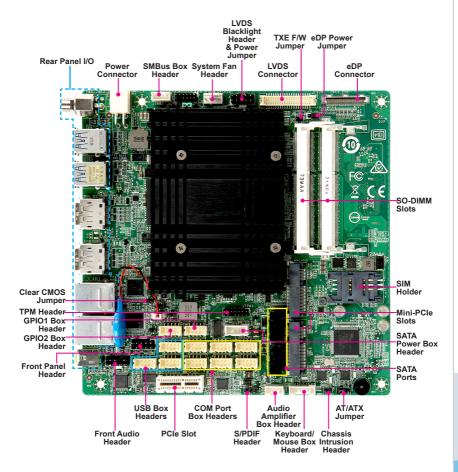

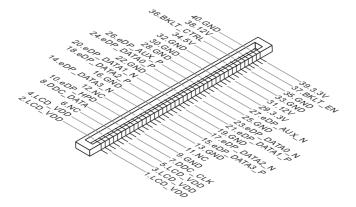

## **Motherboard Layout**

# 2 Hardware Setup

This chapter provides you with the information about hardware setup procedures. While doing the installation, be careful in holding the components and follow the installation procedures. For some components, if you install in the wrong orientation, the components will not work properly.

Use a grounded wrist strap before handling computer components. Static electricity may damage the components.

## **Components Reference Guide**

| Memory                                                     | 2-3  |

|------------------------------------------------------------|------|

| Power Supply                                               | 2-4  |

| System Power Connector: JPWR1                              | 2-4  |

| SATA Power Box Header: JSATA_PWR1                          | 2-4  |

| Rear Panel I/O                                             | 2-5  |

| Connector                                                  | 2-6  |

| Fan Power Header: SYSFAN1                                  | 2-6  |

| Serial ATA Connector: JSATA1, JSATA2                       | 2-6  |

| Chassis Intrusion Header: JCASE1                           |      |

| 3.3V GPIO Box Header: JGPIO1                               | 2-7  |

| 5V GPIO Box Header: JGPIO2                                 | 2-7  |

| Audio Amplifier Box Header: JAMP1                          | 2-8  |

| S/PDIF Header: JSPDI1                                      | 2-8  |

| Front Audio Header: JAUD1                                  | 2-8  |

| Front Panel Header: JFP1                                   | 2-9  |

| Keyboard/Mouse Box Header: JKBMS1                          | 2-9  |

| USB 2.0 Box Headers: JUSB1, JUSB2, JUSB3                   | 2-9  |

| SMBus Box Header: JSMB1                                    | 2-10 |

| LVDS Connector: JLVDS1                                     | 2-10 |

| COM Port Box Headers: JCOM1 ~ JCOM6                        | 2-11 |

| eDP Connector: FPC1_EDP                                    | 2-12 |

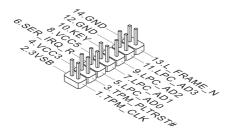

| LPC Debug Port Header: JTPM1 (With TPM Support)            | 2-13 |

| Jumper                                                     | 2-14 |

| Clear CMOS Jumper: JCMOS1                                  | 2-14 |

| AT/ATX Jumper: JATX1                                       | 2-14 |

| TXE F/W Jumper: JTXE1                                      | 2-15 |

| eDP Power Jumper: JEDP_VDD1                                | 2-15 |

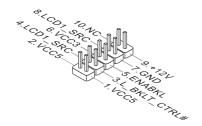

| LVDS Blacklight Header & Power Jumper: JVDD1               | 2-15 |

| Slot                                                       | 2-16 |

| PCIe (Peripheral Component Interconnect Express) Slot      |      |

| Mini PCle (Peripheral Component Interconnect Express) Slot | 2-16 |

| SIM Holder                                                 | 2-16 |

## **Memory**

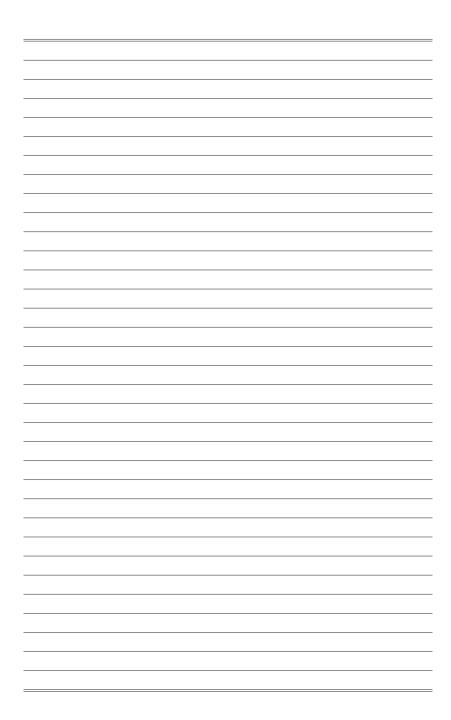

The SO-DIMM slot is intended for memory modules.

Locate the SO-DIMM slot. Align the notch on the DIMM with the key on the slot and to insert the DIMM into the slot.

Push the DIMM gently downwards until the slot levers click and lock the DIMM in place.

#### **Important**

You can barely see the golden finger if the DIMM is properly inserted in the DIMM slot.

To uninstall the DIMM, flip the slot levers outwards and the DIMM will be released instantly.

## **Power Supply**

#### **System Power Connector: JPWR1**

This connector is used to provide power to the system.

#### SATA Power Box Header: JSATA PWR1

This connector is used to provide power to SATA devices.

#### **Important**

Make sure that all power connectors are connected to the power supply to ensure stable operation of the motherboard.

## Rear Panel I/O

#### > DC-In Jack

This jack is used to provide power to the motherboard.

#### > USB 3.2 Gen 1 Port

The USB 3.2 Gen 1 port is backward-compatible with USB 2.0 devices and supports data transfer rate up to 5 Gbit/s (SuperSpeed).

#### ➤ HDMI Port

The High-Definition Multimedia Interface (HDMI) is an all-digital audio/video interface capable of transmitting uncompressed streams. HDMI supports all TV format, including standard, enhanced, or high-definition video, plus multi-channel digital audio on a single cable.

#### > DisplayPort

DisplayPort is a digital display interface standard. This connector is used to connect a monitor with DisplayPort inputs.

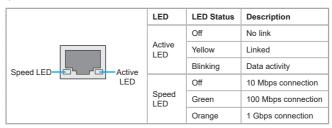

#### ➤ GbE RJ45 Port

The standard single RJ45 LAN jack is provided for connection to the Local Area Network (LAN). You can connect a network cable to it.

#### Line-Out Jack

For speakers or headphones.

#### **Connector**

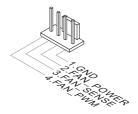

#### Fan Power Header: SYSFAN1

The fan power connectors support system cooling fan with +12V. When connecting the wire to the connectors, always note that the red wire is the positive and should be connected to the +12V; the black wire is Ground and should be connected to GND. If the motherboard has a System Hardware Monitor chipset onboard, you must use a specially designed fan with speed sensor to take advantage of the CPU fan control.

#### **Important**

Fan cooler sets with 3- or 4-pin power connector are both available.

#### Serial ATA Connector: JSATA1, JSATA2

This connector is a high-speed Serial ATA interface port. Each connector can connect to one Serial ATA device.

#### **Important**

Please do not fold the SATA cable into a 90-degree angle. Otherwise, data loss may occur during transmission.

#### Chassis Intrusion Header: JCASE1

This connector connects to the chassis intrusion switch cable. If the computer case is opened, the chassis intrusion mechanism will be activated. The system will record this intrusion and a warning message will flash on screen. To clear the warning, you must enter the BIOS utility and clear the record.

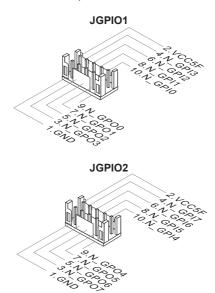

## 3.3V GPIO Box Header: JGPIO1 5V GPIO Box Header: JGPIO2

This connector is provided for the General-Purpose Input/Output (GPIO)

peripheral module.

JGPIO1: 8 bits (4 x GPI; 4 x GPO), 3.3V JGPIO2: 8 bits (4 x GPI; 4 x GPO), 5V

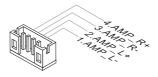

#### **Audio Amplifier Box Header: JAMP1**

The connector is used to connect audio amplifiers to enhance audio performance.

#### S/PDIF Header: JSPDI1

This header is used to connect S/PDIF (Sony & Philips Digital Interconnect Format) interface for digital audio transmission.

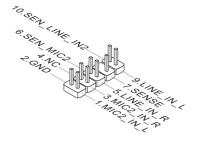

#### Front Audio Header: JAUD1

This connector allows you to connect the front panel audio.

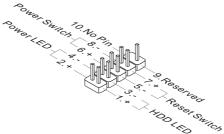

#### Front Panel Header: JFP1

This front panel connector is provided for electrical connection to the front panel switches & LEDs and is compliant with Intel Front Panel I/O Connectivity Design Guide.

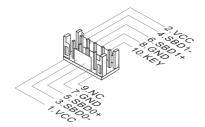

#### Keyboard/Mouse Box Header: JKBMS1

This connector is provided to connect a keyboard and a mouse.

#### USB 2.0 Box Headers: JUSB1, JUSB2, JUSB3

This connector, compliant with Intel I/O Connectivity Design Guide, is ideal for connecting high-speed USB interface peripherals such as USB HDD, digital cameras, MP3 players, printers, modems and the like.

#### **Important**

Note that the pins of VCC and GND must be connected correctly to avoid possible damage.

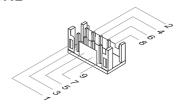

#### SMBus Box Header: JSMB1

This connector, known as I2C, is for users to connect System Management Bus (SMBus) interface.

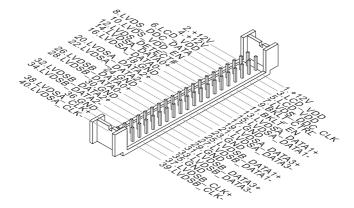

#### LVDS Connector: JLVDS1

The LVDS (Low Voltage Differential Signal) connector provides a digital interface typically used with flat panels. After connecting an LVDS interface flat panel to the JLVDS1, be sure to check the panel datasheet and set the LVDS jumper to proper power voltage.

#### **Important**

Pin 12 is a detect pin. When using a customized LVDS cable, pin 12 should be a signal ground with a low impedance. Otherwise, LVDS will not function.

#### COM Port Box Headers: JCOM1 ~ JCOM6

This connector is a 16550A high speed communications port that sends/receives 16 bytes FIFOs. You can attach a serial device to it.

#### > JCOM1~JCOM2

#### RS232

| 110202 |        |                                   |

|--------|--------|-----------------------------------|

| PIN    | SIGNAL | DESCRIPTION                       |

| 1      | DCD    | Data Carrier Detect               |

| 2      | RXD    | Receive Data                      |

| 3      | TXD    | Transmit Data                     |

| 4      | DTR    | Data Terminal Ready               |

| 5      | GND    | Ground                            |

| 6      | DSR    | Data Set Ready                    |

| 7      | RTS    | Request To Send                   |

| 8      | CTS    | Clear To Send                     |

| 9      | POWER  | 5V or 12V selected by GPIO (BIOS) |

|        |        |                                   |

#### RS422

| PIN | SIGNAL | DESCRIPTION             |

|-----|--------|-------------------------|

| 1   | TXD-   | Transmit Data, Negative |

| 2   | TXD+   | Transmit Data, Positive |

| 3   | RXD+   | Receive Data, Positive  |

| 4   | RXD-   | Receive Data, Negative  |

| 5   | GND    | Ground                  |

| 6   | NC     | No Connection           |

| 7   | NC     | No Connection           |

| 8   | NC     | No Connection           |

| 9   | NC     | No Connection           |

#### RS485

| PIN | SIGNAL | DESCRIPTION    |

|-----|--------|----------------|

| 1   | D-     | Data, Negative |

| 2   | D+     | Data, Positive |

| 3   | NC     | No Connection  |

| 4   | NC     | No Connection  |

| 5   | GND    | Ground         |

| 6   | NC     | No Connection  |

| 7   | NC     | No Connection  |

| 8   | NC     | No Connection  |

| 9   | NC     | No Connection  |

#### > JCOM3~JCOM6

RS232

| PIN | SIGNAL | DESCRIPTION         |

|-----|--------|---------------------|

| 1   | DCD    | Data Carrier Detect |

| 2   | RXD    | Receive Data        |

| 3   | TXD    | Transmit Data       |

| 4   | DTR    | Data Terminal Ready |

| 5   | GND    | Ground              |

| 6   | DSR    | Data Set Ready      |

| 7   | RTS    | Request To Send     |

| 8   | CTS    | Clear To Send       |

| 9   | RI     | Ring Indicator      |

#### eDP Connector: FPC1\_EDP

This connector is for connecting the flat eDP cable.

#### LPC Debug Port Header: JTPM1 (With TPM Support)

This connector works as LPC debug port and supports TPM modules.

## **Jumper**

#### Important

Avoid adjusting jumpers when the system is on; it will damage the motherboard.

#### **Clear CMOS Jumper: JCMOS1**

There is a CMOS RAM onboard that has a power supply from an external battery to keep the data of system configuration. With the CMOS RAM, the system can automatically boot OS every time it is turned on. If you want to clear the system configuration, set the jumper to clear data.

#### Important

You can clear CMOS by shorting 2-3 pin while the system is off. Then return to 1-2 pin position. Avoid clearing the CMOS while the system is on; it will damage the motherboard.

#### AT/ATX Jumper: JATX1

This jumper allows users to select between AT and ATX power.

#### **TXE F/W Jumper: JTXE1**

This jumper is used to enable/disable the Intel TXE F/W.

#### eDP Power Jumper: JEDP\_VDD1

Use this jumper to specify the operation voltage of the eDP interface flat panel.

#### LVDS Blacklight Header & Power Jumper: JVDD1

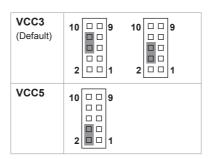

The connector is provided for LCD backlight options and allows users to select the operation voltage of the LVDS flat panel.

#### Slot

#### PCIe (Peripheral Component Interconnect Express) Slot

The PCI Express slot supports PCIe interface expansion cards.

PCle x1 slot

## Mini PCIe (Peripheral Component Interconnect Express) Slot

The Mini PCIe slot is provided for WiFi modules, Bluetooth modules, TV tuner cards and other Mini-PCIe cards.

- MINI PCIE1: full/half size, with SIM holder

- MINI PCIE2: mSATA only, colay onboard SATA2

#### SIM Holder

This holder is provided for SIM cards.

Holder

#### **Important**

When adding or removing expansion cards, make sure that you unplug the power supply first. Meanwhile, read the documentation for the expansion card to configure any necessary hardware or software settings for the expansion card, such as jumpers, switches or BIOS configuration.

# 3 BIOS Setup

This chapter provides information on the BIOS Setup program and allows users to configure the system for optimal use.

Users may need to run the Setup program when:

- An error message appears on the screen at system startup and requests users to run SETUP.

- Users want to change the default settings for customized features.

#### **Important**

- Please note that BIOS update assumes technician-level experience.

- As the system BIOS is under continuous update for better system performance, the illustrations in this chapter should be held for reference only.

## **Entering Setup**

Power on the computer and the system will start POST (Power On Self Test) process. When the message below appears on the screen, press <DEL> or <F2> key to enter Setup.

#### Press <DEL> or <F2> to enter SETUP

If the message disappears before you respond and you still wish to enter Setup, restart the system by turning it OFF and On or pressing the RESET button. You may also restart the system by simultaneously pressing <Ctrl>, <Alt>, and <Delete> keys.

#### **Important**

The items under each BIOS category described in this chapter are under continuous update for better system performance. Therefore, the description may be slightly different from the latest BIOS and should be held for reference only.

#### **Control Keys**

| $\leftarrow \rightarrow$ | Select Screen      |

|--------------------------|--------------------|

| $\uparrow \downarrow$    | Select Item        |

| Enter                    | Select             |

| + -                      | Change Option      |

| F1                       | General Help       |

| F7                       | Previous Values    |

| F9                       | Optimized Defaults |

| F10                      | Save & Reset       |

| Esc                      | Exit               |

#### **Getting Help**

After entering the Setup menu, the first menu you will see is the Main Menu.

#### Main Menu

The main menu lists the setup functions you can make changes to. You can use the arrow keys (  $\uparrow\downarrow$  ) to select the item. The on-line description of the highlighted setup function is displayed at the bottom of the screen.

#### Sub-Menu

If you find a right pointer symbol appears to the left of certain fields that means a sub-menu can be launched from this field. A sub-menu contains additional options for a field parameter. You can use arrow keys (  $\uparrow\downarrow$  ) to highlight the field and press <Enter> to call up the sub-menu. Then you can use the control keys to enter values and move from field to field within a sub-menu. If you want to return to the main menu, just press the <Esc>.

#### General Help <F1>

The BIOS setup program provides a General Help screen. You can call up this screen from any menu by simply pressing <F1>. The Help screen lists the appropriate keys to use and the possible selections for the highlighted item. Press <Esc> to exit the Help screen.

#### The Menu Bar

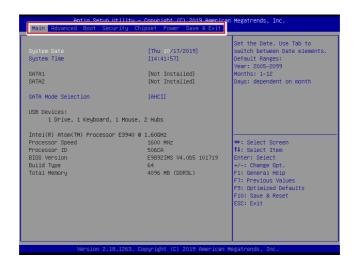

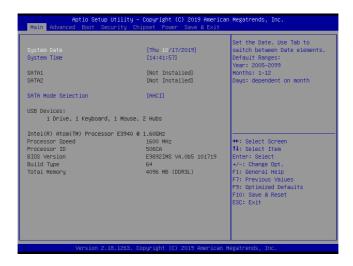

#### ▶ Main

Use this menu for basic system configurations, such as time, date, etc.

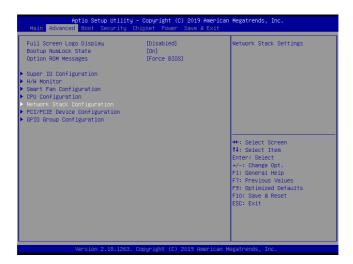

#### ► Advanced

Use this menu to set up the items of special enhanced features.

#### ▶ Boot

Use this menu to specify the priority of boot devices.

#### ▶ Security

Use this menu to set supervisor and user passwords.

#### Chipset

This menu controls the advanced features of the onboard chipsets.

#### ▶ Power

Use this menu to specify your settings for power management.

#### ► Save & Exit

This menu allows you to load the BIOS default values or factory default settings into the BIOS and exit the BIOS setup utility with or without changes.

#### Main

#### ► System Date

This setting allows you to set the system date. The date format is <Day>, <Month> <Date> <Year>.

#### ► System Time

This setting allows you to set the system time. The time format is <Hour> <Minute> <Second>.

#### ► SATA Mode Selection

This setting specifies the SATA controller mode.

#### **Advanced**

#### ► Full Screen Logo Display

This BIOS feature determines if the BIOS should hide the normal POST messages with the motherboard or system manufacturer's full-screen logo.

When it is enabled, the BIOS will display the full-screen logo during the boot-up sequence, hiding normal POST messages.

When it is disabled, the BIOS will display the normal POST messages, instead of the full-screen logo.

Please note that enabling this BIOS feature often adds 2-3 seconds of delay to the booting sequence. This delay ensures that the logo is displayed for a sufficient amount of time. Therefore, it is recommended that you disable this BIOS feature for a faster boot-up time.

#### ▶ Bootup NumLock State

This setting is to set the Num Lock status when the system is powered on. Setting to [On] will turn on the Num Lock key when the system is powered on. Setting to [Off] will allow users to use the arrow keys on the numeric keypad.

#### ▶ Option ROM Messages

This item is used to determine the display mode when an optional ROM is initialized during POST. When set to [Force BIOS], the display mode used by AMI BIOS is used. Select [Keep Current] if you want to use the display mode of optional ROM.

#### ► Super IO Configuration

#### ► Serial Port 1/2/3/4/5/6

This setting enables/disables the specified serial port.

#### ▶ Change Settings

This setting is used to change the address & IRQ settings of the specified serial port.

#### ▶ Mode Select

Select an operation mode for the specified serial port.

#### ► FIFO Mode

This setting controls the FIFO data transfer mode.

#### ► Shared IRQ Mode

This setting provides the system with the ability to share interrupts among its serial ports.

#### ► Watch Dog Timer

You can enable the system watch-dog timer, a hardware timer that generates a reset when the software that it monitors does not respond as expected each time the watch dog polls it.

#### ► H/W Monitor

These items display the current status of all monitored hardware devices/ components such as voltages, temperatures and all fans' speeds.

#### ▶ Smart Fan Configuration

#### ► Smart SYSFAN Target

This setting enables/disables the Smart Fan function. Smart Fan is an excellent feature which will adjust the CPU/system fan speed automatically depending on the current CPU/system temperature, avoiding the overheating to damage your system.

## ► CPU Configuration

## ► Intel Virtualization Technology

Virtualization enhanced by Intel Virtualization Technology will allow a platform to run multiple operating systems and applications in independent partitions. With virtualization, one computer system can function as multiple "Virtual" systems.

## ► EIST

EIST (Enhanced Intel SpeedStep Technology) allows the system to dynamically adjust processor voltage and core frequency, which can result in decreased average power consumption and decreased average heat production. When disabled, the processor will return the actual maximum CPUID input value of the processor when queried.

## ► C-States

C-state performance indicates the ability to run the processor in lower power states when the PC is idle. This setting enables/disables the C-State Configuration for power saving purposes.

## ▶ Network Stack Configuration

This menu provides Network Stack settings for users to enable network boot (PXE) from BIOS.

## ▶ Network Stack

When this setting is set to [Enabled], the system will boot via the network instead of a disk drive.

## ► PCI/PCIE Device Configuration

## ► Legacy USB Support

Set to [Enabled] if you need to use any USB 1.1/2.0 device in the operating system that does not support or have any USB 1.1/2.0 driver installed, such as DOS and SCO Unix.

## ► Audio Controller

This setting enables/disables the onboard audio controller.

## ► Launch OnBoard LAN OpROM

These settings enable/disable the initialization of the onboard/onchip LAN Boot ROM during bootup. Selecting [Disabled] will speed up the boot process.

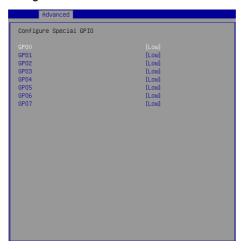

## ► GPIO Group Configuration

## ► GPO0 ~ GPO7

These settings control the operation mode of the specified GPIO.

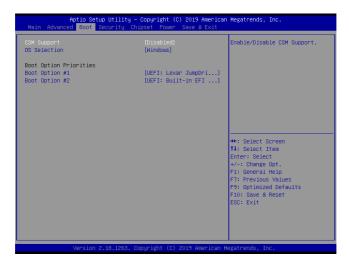

## **Boot**

## ► CSM Support

This setting enables/disables the support for Compatibility Support Module, a part of the Intel Platform Innovation Framework for EFI providing the capability to support legacy BIOS interfaces.

## **▶ OS Selection**

This setting allows users to select the Operating System.

## ► Boot Option Priorities

This setting allows users to set the sequence of boot devices where BIOS attempts to load the disk operating system.

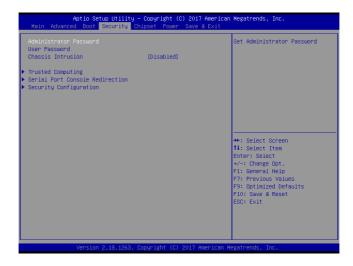

# **Security**

## ► Administrator Password

Administrator Password controls access to the BIOS Setup utility.

## ▶ User Password

User Password controls access to the system at boot and to the BIOS Setup utility.

## ► Chassis Intrusion

The field enables or disables the feature of recording the chassis intrusion status and issuing a warning message if the chassis is once opened.

## ► Trusted Computing

## ► Security Device Support

This setting enables/disables BIOS support for security device. When set to [Disable], the OS will not show security device. TCG EFI protocol and INT1A interface will not be available.

## ► SHA-1 PCR Bank, SHA256 PCR Bank

These settings enable/disable the SHA-1 PCR Bank and SHA256 PCR Bank.

## ▶ Pending Operation

This setting shows pending operation.

## ▶ Platform Hierarchy, Storage Hierarchy, Endorsement Hierarchy

These settings enable/disable the Platform Hierarchy, Storage Hierarchy and Endorsement Hierarchy.

## ▶ TPM2.0 UEFI Spec Version, Physical Presence Spec Version

This settings show the TPM2.0 UEFI Spec Version and Physical Presence Spec Version.

## ► TPM2.0 Interface Type

This setting shows the TPM2.0 Interface Type.

## ▶ Device Select

This setting allows users to select the security device.

## ▶ Disable Block Sid

This setting enables/disables Block SID support, the specification that covers firmware and OS communication to handle freeze-locking events for a self-encrypting hard drive.

## ▶ Serial Port Console Redirection

## ► Console Redirection

Console Redirection operates in host systems that do not have a monitor and keyboard attached. This setting enables/disables the operation of console redirection. When set to [Enabled], BIOS redirects and sends all contents that should be displayed on the screen to the serial COM port for display on the terminal screen. Besides, all data received from the serial port is interpreted as keystrokes from a local keyboard.

## ▶ Console Redirection Settings

## ► Terminal Type

To operate the system's console redirection, you need a terminal supporting ANSI terminal protocol and a RS-232 null modem cable connected between the host system and terminal(s). This setting specifies the type of terminal device for console redirection

## ▶ Bits per second, Data Bits, Parity, Stop Bits

This setting specifies the transfer rate (bits per second, data bits, parity, stop bits) of Console Redirection.

## ▶ Flow Control

Flow control is the process of managing the rate of data transmission between two nodes. It's the process of adjusting the flow of data from one device to another to ensure that the receiving device can handle all of the incoming data. This is particularly important where the sending device is capable of sending data much faster than the receiving device can receive it.

## ▶ VT-UTF8 Combo Key Support

This setting enables/disables the VT-UTF8 combination key support for ANSI/VT100 terminals.

## ▶ Recorder Mode, Resolution 100x31

These settings enable/disable the recorder mode and the resolution 100x31.

## Putty Keypad

PuTTY is a terminal emulator for Windows. This setting controls the numeric keypad for use in PuTTY.

## ► Security Configuration

## ► TXE FW Version

The setting shows the firmware information of the Intel Trusted Execution Engine (TXE).

## ► TXE HMRFPO

The setting enables/disables TXE HMRFPO (Host ME Region Flash Protection Override).

## ►TXE EOP Message

This setting determines whether or not to send EOP (Exchange Online Protection) message before entering OS.

# **Chipset**

## ► DVMT Pre-Allocated

This setting defines the DVMT pre-allocated memory. Pre-allocated memory is the small amount of system memory made available at boot time by the system BIOS for video. Pre-allocated memory is also known as locked memory. This is because it is "locked" for video use only and as such, is invisible and unable to be used by the operating system.

## ► DVMT Total Gfx Mem

This setting specifies the memory size for DVMT.

## ► LCD Panel Type

This setting specifies the LCD panel type.

## ► LVDS Backlight Control

This setting controls the intensity of the LVDS backlight.

## ► LVDS

This setting enables/disables the LVDS interface.

## **Power**

## ▶ Restore AC Power Loss

This setting specifies whether your system will reboot after a power failure or interrupt occurs. Available settings are:

| [Power Off]  | Leaves the computer in the power off state.                                            |

|--------------|----------------------------------------------------------------------------------------|

| [Power On]   | Leaves the computer in the power on state.                                             |

| [Last State] | Restores the system to the previous status before power failure or interrupt occurred. |

## ▶ Deep Sleep Mode

The setting enables/disables the Deep S5 power saving mode. S5 is almost the same as G3 Mechanical Off, except that the PSU still supplies power, at a minimum, to the power button to allow return to S0. A full reboot is required. No previous content is retained. Other components may remain powered so the computer can "wake" on input from the keyboard, clock, modem, LAN, or USB device.

## \*\* Advanced Resume Events Control \*\*

#### ► PCIE PME

This field specifies whether the system will be awakened from power saving modes when activity or input signal of onboard PCIE PME is detected.

## ► USB from S3/S4

The item allows the activity of the USB device to wake up the system from S3/S4 sleep state.

## ► RTC

When [Enabled], your can set the date and time at which the RTC (real-time clock) alarm awakens the system from suspend mode.

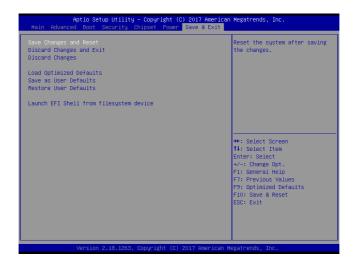

## Save & Exit

## ► Save Changes and Reset

Save changes to CMOS and reset the system.

## ► Discard Changes and Exit

Abandon all changes and exit the Setup Utility.

## ► Discard Changes

Abandon all changes.

## ► Load Optimized Defaults

Use this menu to load the default values set by the motherboard manufacturer specifically for optimal performance of the motherboard.

#### ▶ Save as User Defaults

Save changes as the user's default profile.

#### ▶ Restore User Defaults

Restore the user's default profile.

## ► Launch EFI Shell from filesystem device

This setting helps to launch the EFI Shell application from one of the available file system devices.

# Appendix GPIO WDT BKL Programming

This appendix provides WDT (Watch Dog Timer), GPIO (General Purpose Input/ Output) and LVDS Backlight programming guide.

## **Abstract**

## **Abstract**

In this document, code examples based on C programming language are provided for customer interest. **Inportb, Outportb, Inportl** and **Outportl** are basic functions used for access IO ports and defined as following.

Inportb: Read a single 8-bit I/O port.

Outportb: Write a single byte to an 8-bit port.

InportI: Reads a single 32-bit I/O port.

Outportl: Write a single long to a 32-bit port.

## **General Purposed IO**

## 1. General Purposed IO - GPIO/DIO

| The GPIO port configuration addresses are listed in the following table | The GPIO por | rt configuration | addresses are | listed in th | e following table: |

|-------------------------------------------------------------------------|--------------|------------------|---------------|--------------|--------------------|

|-------------------------------------------------------------------------|--------------|------------------|---------------|--------------|--------------------|

| Name    | IO Port | IO address | Name    | IO Port | IO address |

|---------|---------|------------|---------|---------|------------|

| N_GPI0  | 0xA02   | Bit 0      | N_GPO0  | 0xA02   | Bit 4      |

| N_GPI1  | 0xA02   | Bit 1      | N_GPO1  | 0xA02   | Bit 5      |

| N_GPI2  | 0xA02   | Bit 2      | N_GPO2  | 0xA02   | Bit 6      |

| N_GPI3  | 0xA02   | Bit 3      | N_GPO3  | 0xA02   | Bit 7      |

| N_GPI4* | 0x12    | Bit 6      | N_GPO4* | 0x21    | Bit 6      |

| N_GPI5* | 0x12    | Bit 4      | N_GPO5* | 0x21    | Bit 7      |

| N_GPI6* | 0x12    | Bit 1      | N_GPO6* | 0x11    | Bit 5      |

| N_GPI7  | 0xA03   | Bit 0      | N_GPO7* | 0x41    | Bit 0      |

Note\*: Based on hardware design, N\_GPI4 ~ NGPI6 and N\_GPO4 ~ N\_GPO7 should be accessed through controller device 0x6E on SMBus. The associated access method in examples (SMBus\_ReadByte, SMBus\_WriteByte) are provided in part 4.

## 1.1 Set output value of GPO

- 1. Read the value from GPO port.

- 2. Set the value of GPO address.

- 3. Write the value back to GPO port.

```

Example: Set N_GPO0 output "high"

val = Inportb (0xA02);

// Read value from N_GPO0 port.

val = val | (1<<4);

// Set N_GPO0 address (bit 4) to 1 (output "high").

Outportb (0xA02, val);

// Write back to N_GPO0 port.

Example: Set N_GPO1 output "low"

val = Inportb (0xA02);

// Read value from N GPO1 port.

val = val & (~(1<<5));

// Set N_GPO1 address (bit 5) to 0 (output "low").

Outportb (0xA02, val);

// Write back to N GPO1 port.

Example: Set N_GPO4 output "high"

Val =SMBus_ReadByte (0x6E, 0x21); // Read value from N_GPO4 port through SMBus.

// Set N_GPO4 address (bit 5) to 1 (output "high").

val = val | (1<<6);

SMBus_WriteByte (0x6E, 0x12, val); // Write back to N_GPO4 port through SMBus.

```

## 1.2 Read input value from GPI:

- 1. Read the value from GPI port.

- 2. Get the value of GPI address.

```

Example: Get N_GPI2 input value.

val = Inportb (0xA02); // Read value from N_GPI2 port.

val = val & (1<<2); // Read N_GPI2 address (bit 2).

if (val) printf ("Input of N_GPI2 is High");

```

printf ("Input of N\_GPI2 is Low");

## Example: Get N\_GPI6 input value.

else

```

val = SMBus_ReadByte (0x6E, 0x12); // Read value from N_GPI6 port through SMBus.

val = val & (1<<1); // Read N_GPI6 address (bit 1).

if (val) printf ("input of N_GPI6 is High");

else printf ("input of N_GPI6 is Low");</pre>

```

# **Watchdog Timer**

## 2. Watchdog Timer - WDT

The base address (WDT\_BASE) of WDT configuration registers is 0xA10.

#### 2.1 Set WDT Time Unit

#### 2.2 Set WDT Time

```

Outportb (WDT_BASE + 0x06, Time); // Write WDT time, value 1 to 255.

```

#### 2.3 Enable WDT

## 2.4 Disable WDT

#### 2.5 Check WDT Reset Flag

If the system has been reset by WDT function, this flag will set to 1.

## 2.6 Clear WDT Reset Flag

```

val = Inportb (WDT_BASE + 0x05);  // Read current WDT setting

val = val | 0x40;  // Set 1 to WDTMOUT_STS (bit 6);

Outportb (WDT_BASE + 0x05, val);  // Write back WDT setting

```

# **LVDS Backlight Brightness Control**

## 3. LVDS Backlight Brightness Control

The LVDS controller support 17 level of backlight brightness value from 0 (30%) to 16 (100%) and it is accessible through SMBus. The associated access method (SMBus\_ReadByte, SMBus\_WriteByte) are provided in part 4.

## 3.1 Set the Level of LVDS Backlight

- 1. Write OxED into address Ox7F on SMBus device Ox42.

- Write desired backlight level from 0x0 (30%) to 0x10 (100%) into address 0x6E on SMBus device 0x42.

```

Example: Set LVDS backlight level to 0x10 (100%)

SMBus_WriteByte (0x42, 0x7F, 0xED);

SMBus_WriteByte (0x42, 0x6E, 0x10); // Set brightness to 100%

```

## 3.2 Read the Level of LVDS Backlight

- 1. Write OxED into address Ox7F on SMBus device Ox42.

- 2. Read current backlight level from address Ox6E on SMBus device Ox42.

```

Example: Get LVDS backlight level

SMBus_WriteByte (0x42, 0x7F, 0xED);

BKL_Value = SMBus_ReadByte (0x42, 0x6E);

```

## **SMBus Access**

## 4. SMBus Access

The base address of SMBus must be known before access. The relevant bus and device information are as following.

```

#define IO_SC 0xCF8

#define IO_DA 0xCFC

#define PCIBASEADDRESS 0x80000000

#define PCI_BUS_NUM 0

#define PCI_DEV_NUM 31

#define PCI_FUN_NUM 1

```

## 4.1 Get SMBus Base Address

## 4.2 SMBus\_ReadByte (char DEVID, char offset)

Read the value of OFFSET from SMBus device DEVID.

```

Outportb (LOWORD (SMBUS_BASE), 0xFE);

Outportb (LOWORD (SMBUS_BASE) + 0x04, DEVID + 1); //out Base + 04, (DEVID + 1)

Outportb (LOWORD (SMBUS_BASE) + 0x03, OFFSET); //out Base + 03, OFFSET

Outportb (LOWORD (SMBUS_BASE) + 0x02, 0x48); //out Base + 02, 48H

mdelay (20); //delay 20ms to let data ready

while ((Inportl (SMBUS_BASE) & 0x01) != 0); //wait SMBus ready

SMB_DATA = Inportb (LOWORD (SMBUS_BASE) + 0x05); //input Base + 05

```

## 4.3 SMBus\_WriteByte (char DEVID, char offset, char DATA)

Write DATA to OFFSET on SMBus device DEVID.

```

Outportb (LOWORD (SMBUS_BASE), 0xFE);

Outportb (LOWORD (SMBUS_BASE) + 0x04, DEVID); //out Base + 04, (DEVID)

Outportb (LOWORD (SMBUS_BASE) + 0x03, OFFSET); //out Base + 03, OFFSET

Outportb (LOWORD (SMBUS_BASE) + 0x05, DATA); //out Base + 05, DATA

Outportb (LOWORD (SMBUS_BASE) + 0x02, 0x48); //out Base + 02, 48H

mdelay (20); //wait 20ms

```