innodisk

# icf 1se

| Customer:          |  |

|--------------------|--|

| Customer           |  |

| Part<br>Number:    |  |

| Innodisk           |  |

| Part<br>Number:    |  |

| Innodisk           |  |

| <b>Model Name:</b> |  |

| Date:              |  |

|                    |  |

# Innodisk Customer Approver Approver

# Total Solution For Industrial Flash Storage

### **Table of contents**

| 1. PRODUCT OVERVIEW                                                      | 8  |

|--------------------------------------------------------------------------|----|

| 1.1 Introduction of Innodisk iCF 1SE                                     | 8  |

| 1.2 PRODUCT VIEW AND MODELS                                              |    |

| 2. PRODUCT SPECIFICATIONS                                                | 9  |

| 4. PIN DESCRIPTION                                                       | 12 |

| 5. SPECIFICATIONS                                                        |    |

| 5.1 CE AND FCC COMPATIBILITY                                             | 20 |

| 5.2 CE AND FCC COMPATIBILITY                                             | 20 |

| 5.3 Environmental Specifications                                         | 20 |

| 5.3.1 Temperature Ranges                                                 | 20 |

| 5.3.2 Humidity                                                           | 20 |

| 5.3.3 Insertion                                                          | 20 |

| 5.3.4 Shock and Vibration                                                | 20 |

| 5.3.5 Mean Time between Failures (MTBF)                                  | 20 |

| 5.4 ERROR DETECTION AND CORRECTION                                       | 21 |

| 5.5 WEAR-LEVELING                                                        | 21 |

| 5.6 NAND FLASH MEMORY AND ENDURANCE                                      | 21 |

| 5.7 RELIABILITY                                                          | 21 |

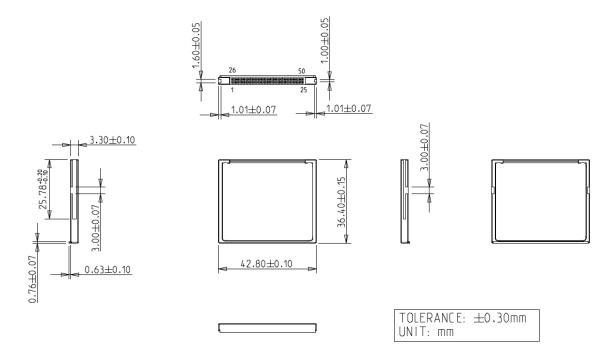

| 5.8 MECHANICAL DIMENSIONS                                                | 22 |

| 5.9 ELECTRICAL SPECIFICATIONS                                            | 22 |

| 5.9.1 DC Characteristic                                                  | 22 |

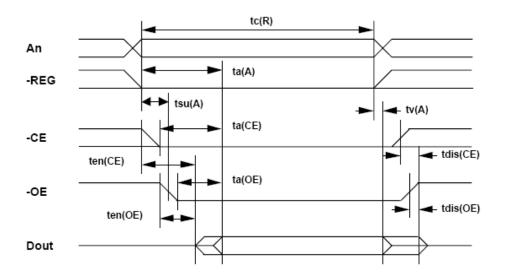

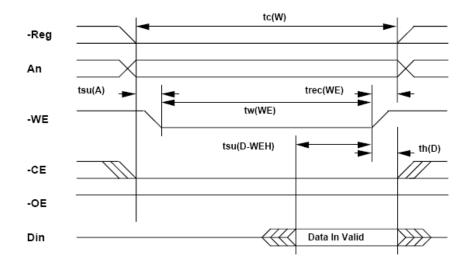

| 5.9.2 Timing Specifications                                              | 22 |

| 5.10 Transfer Function                                                   | 36 |

| 5.10.1 I/O Transfer function                                             | 36 |

| 5.10.2 Common Memory Transfer Function                                   | 37 |

| 5.10.3 True IDE Mode I/O Transfer Function                               | 38 |

| 5.11 CONFIGURATION REGISTER                                              | 39 |

| 5.11.1 Configuration Option Register (200h in Attribute Memory)          | 39 |

| 5.11.2 Card Configuration and Status Register (202h in Attribute Memory) | 40 |

| 5.11.3 Pin Replacement register (204h in Attribute Memory)               | 41 |

| 5.11.4 Socket and Copy Register (206h in Attribute Memory)               | 41 |

| 5.12 SOFTWARE INTERFACE                                                  | 42 |

| 5.12.1 CF-ATA Drive Register Set Definition and Protocol                 |    |

| 5.12.2 I/O Primary and Secondary Address Configurations                  | 43 |

| 5.12.3 Contiguous I/O Mapped Addressing                                  |    |

| 5.12.4 Memory Mapped Addressing                                          |    |

| 5.12.5 True IDE Mode Addressing                                          | 46 |

6.

| 5.12.6 CF-ATA Register                                           | 46 |

|------------------------------------------------------------------|----|

| 5.13 HARDWARE RESET(ONLY FOR MEMORY CARD MODE AND I/O CARD MODE) | 51 |

| 5.14 Power on Reset                                              | 52 |

| 5.15 SUPPORTED IDE COMMANDS                                      | 52 |

| 5.15.1 Check power mode – 98H or E5H                             | 54 |

| 5.15.2 Execute Device Diagnostic – 90H                           | 54 |

| 5.15.3 Erase Sector(s) – C0H                                     | 55 |

| 5.15.4 Format Track – 50H                                        | 55 |

| 5.15.5 Identify Device – ECH                                     | 56 |

| 5.15.6 Idle -97H or E3H                                          | 64 |

| 5.15.7 Idle immediate - 95H or E1H                               | 64 |

| 5.15.8 Initialize Device Parameters - 91H                        | 65 |

| 5.15.9 Read Buffer - E4H                                         | 65 |

| 5.15.10 Read DMA - C8H                                           | 65 |

| 5.15.11 Read Long Sector - 22H or 23H                            | 66 |

| 5.15.12 Read Sector(s) - 20H or 21H                              | 67 |

| 5.15.13 Read Verify Sector(s) - 40H or 41H                       | 67 |

| 5.15.14 Recalibrate - 1XH                                        | 68 |

| 5.15.15 Request Sense - 03H                                      | 68 |

| 5.15.16 Seek - 7XH                                               | 69 |

| 5.15.17 Set Features – EFH                                       | 69 |

| 5.15.18 Set Sleep Mode - 99H or E6H                              | 70 |

| 5.15.19 Standby - 96H or E2H                                     | 71 |

| 5.15.20 Standby Immediate - 94H or E0H                           | 71 |

| 5.15.21 Write Buffer - E8H                                       | 71 |

| 5.15.22 Write DMA - CAH                                          | 72 |

| 5.12.23 Write Sector(s) - 30H or 31H                             | 73 |

| 5.16 DEVICE PARAMETERS                                           | 74 |

| INNODISK PART NUMBER RULE                                        | 75 |

|                                                                  |    |

# **REVISION HISTORY**

| Revision | Description                                       | Date       |  |  |  |  |

|----------|---------------------------------------------------|------------|--|--|--|--|

| 1.0      | Release First Version                             | Oct. 2013  |  |  |  |  |

| 1.1      | Modify performance Sep. 2014                      |            |  |  |  |  |

| 1.2      | Add CE/FCC certification                          | Oct. 2014  |  |  |  |  |

| 1.3      | Modify TBW based on NAND Flash specifications     | Jan. 2015  |  |  |  |  |

| 1.4      | Modify the minimum capacities.                    | Feb. 2015  |  |  |  |  |

| 1.5      | Modify the PIO mode support 0-6                   | Mar. 2015  |  |  |  |  |

|          | Add Appendix                                      |            |  |  |  |  |

| 1.6      | Edit part number description.                     | Jul. 2016  |  |  |  |  |

| 1.7      | Updated CE/FCC certification (EN 55032) Apr. 2017 |            |  |  |  |  |

| 1.8      | Update tsuA(IOWR) Jan. 2020                       |            |  |  |  |  |

| 1.9      | Revise True IDE Mode I/O Decoding Info. Oct. 2021 |            |  |  |  |  |

|          | Remove Appendix                                   |            |  |  |  |  |

| 2.0      | Update Mechanical Dimensions Oct., 2024           |            |  |  |  |  |

| 2.1      | Update Product View Jan., 2024                    |            |  |  |  |  |

| 2.2      | Update Mechanical Dimensions                      | Mar., 2025 |  |  |  |  |

### **List of Tables**

| TABLE 1: SHOCK/VIBRATION TEST FOR ICF 1SE                          | 20 |

|--------------------------------------------------------------------|----|

| TABLE 2: ICF 1SE MTBF                                              | 21 |

| TABLE 3: ATTRIBUTE MEMORY READ TIMING                              | 22 |

| Table 4: Configuration Register (Attribute Memory) Write Timing    | 23 |

| Table 5: Common Memory Read Timing                                 | 24 |

| Table 6: Common Memory Write Timing                                | 25 |

| Table 7: I/O Read Timing                                           | 26 |

| Table 8: I/O Write Timing                                          | 28 |

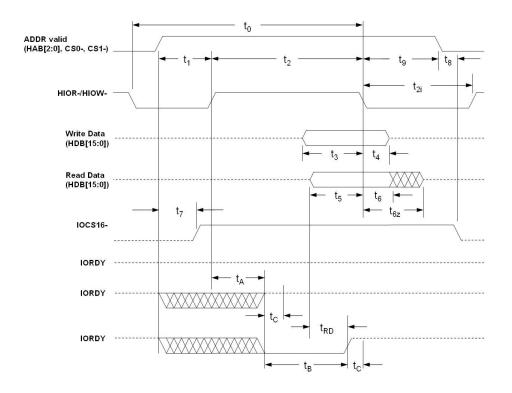

| TABLE 9: READ/WRITE TIMING SPECIFICATIONS, PIO MODE 0-6            | 30 |

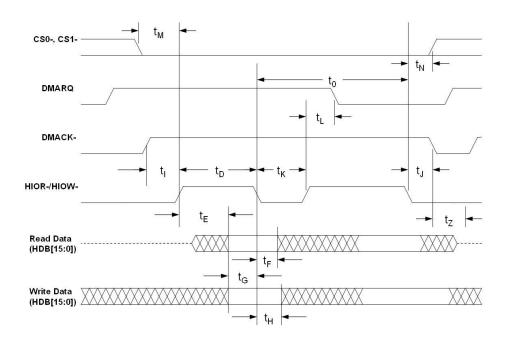

| Table 10: Read/Write Timing Specifications, Multiword DMA Mode 0-4 | 32 |

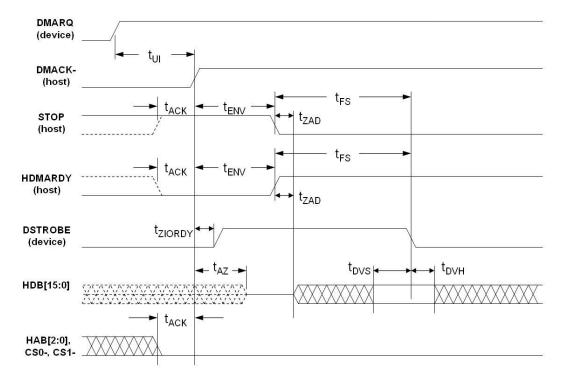

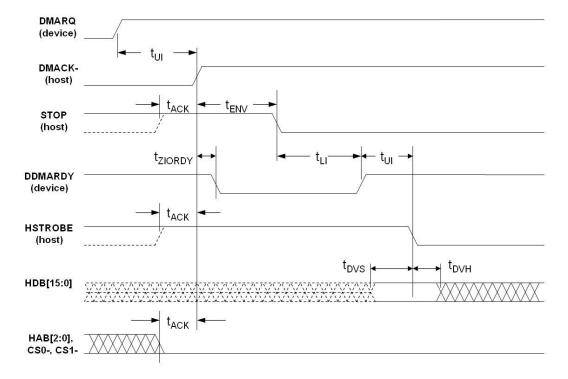

| TABLE 11: TIMING DIAGRAM, ULTRA DMA MODE 0-4                       | 34 |

| TABLE 12: PCMCIA MODE I/O FUNCTION                                 | 36 |

| Table 13: Common Memory Function                                   | 37 |

| TABLE 14: TRUE IDE MODE I/O FUNCTION                               | 38 |

| Table 15: Configuration Option Register                            | 39 |

| Table 16: Information for Configuration Option Register            | 39 |

| Table 17: ICF 1SE Configuration                                    | 39 |

| Table 18: Card Configuration and Status Register                   | 40 |

| Table 19: Information for Card Configuration and Status Register   | 40 |

| TABLE 20: PIN REPLACEMENT REGISTER                                 | 41 |

| TABLE 21: INFORMATION FOR PIN REPLACEMENT REGISTER                 | 41 |

| TABLE 22: PIN REPLACEMENT REGISTER                                 | 41 |

| TABLE 23: INFORMATION FOR PIN REPLACEMENT REGISTER                 | 41 |

| TABLE 24: SOCKET AND COPY REGISTER                                 | 42 |

| TABLE 25: INFORMATION FOR SOCKET AND COPY REGISTER                 | 42 |

| Table 26: I/O Configuration                                        | 42 |

| TABLE 27: PRIMARY AND SECONDARY I/O DECODING                       | 43 |

| TABLE 28: CONTIGUOUS I/O DECODING                                  | 43 |

| TABLE 29: MEMORY MAPPED DECODING                                   | 44 |

| TABLE 30: TRUE IDE MODE I/O DECODING                               | 46 |

| Table 31: Data Register                                            | 47 |

| TABLE 32: ERROR REGISTER                                           | 47 |

| Table 33: Feature Register                                         | 47 |

| TABLE 34: SECTOR COUNT REGISTER                                    | 47 |

| TABLE 35: SECTOR NUMBER REGISTER                                   | 48 |

| Table 36: Cylinder Low Register                                    | 48 |

| Table 37: Cylinder High Register                                   | 48 |

| TABLE 38: DEVICE/HEAD REGISTER                                     | 48 |

| Table 39: Status Register                                          | 49 |

| TABLE 40: DEVICE CONTROL REGISTER            | 50 |

|----------------------------------------------|----|

| Table 41: Drive Address Register             | 50 |

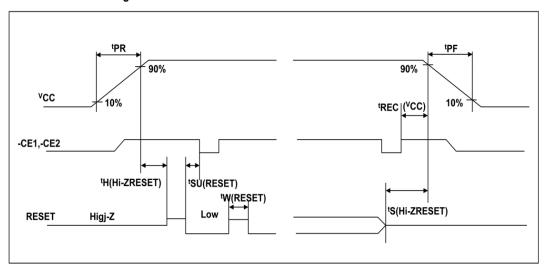

| Table 42: Timing Diagram, Hardware Reset     | 51 |

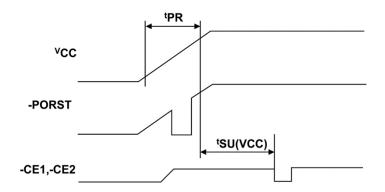

| Table 43: Timing Diagram, Power On Reset     | 52 |

| TABLE 44: TIMING SPECIFICATION FOR EACH MODE | 52 |

| TABLE 45: IDE COMMANDS                       | 52 |

| Table 46: Diagnostic                         | 55 |

| TABLE 47: IDENTIFY DEVICE INFORMATION        | 56 |

| Table 48: Extended Error Codes               | 68 |

| TABLE 49: FEATURE SUPPORTED                  | 70 |

| Table 50: Device parameters                  | 74 |

# **List of Figures**

| FIGURE 1: INNODISK ICF 1SE                                               |    |

|--------------------------------------------------------------------------|----|

| FIGURE 2: MECHANICAL DIMENSION OF ICF 1SE                                | 22 |

| FIGURE 3: ATTRIBUTE MEMORY READ TIMING DIAGRAM                           | 23 |

| FIGURE 4: CONFIGURATION REGISTER (ATTRIBUTE MEMORY) WRITE TIMING DIAGRAM | 2  |

| FIGURE 5: COMMON MEMORY READ TIMING DIAGRAM                              | 25 |

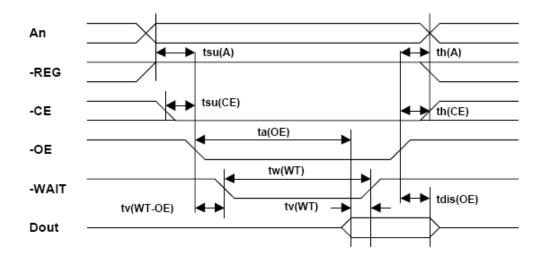

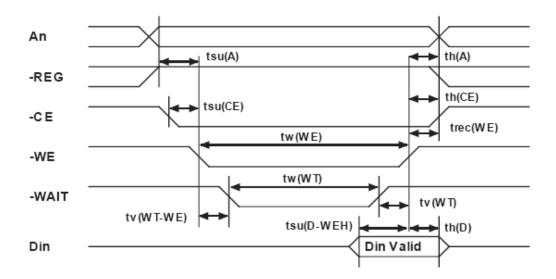

| FIGURE 6: COMMON MEMORY WRITE TIMING DIAGRAM                             | 20 |

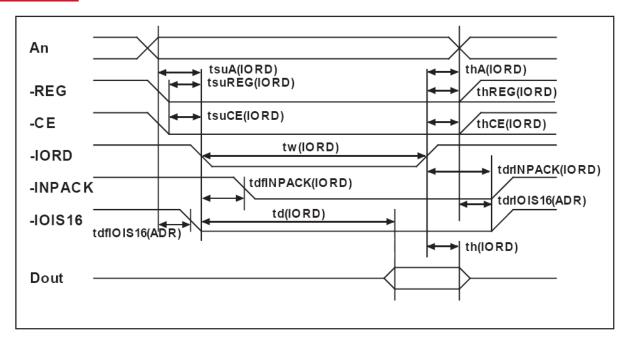

| FIGURE 7: I/O READ TIMING DIAGRAM                                        | 28 |

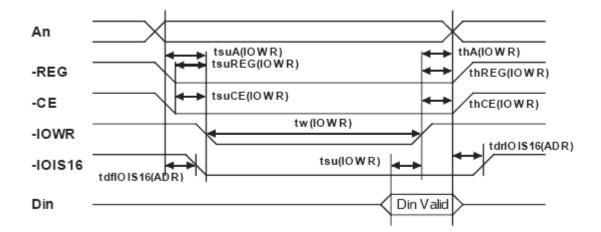

| FIGURE 8: I/O WRITE TIMING DIAGRAM                                       | 29 |

| FIGURE 9: READ/WRITE TIMING DIAGRAM, PIO MODE                            | 30 |

| FIGURE 10: READ/WRITE TIMING DIAGRAM, MULTIWORD DMA MODE                 | 31 |

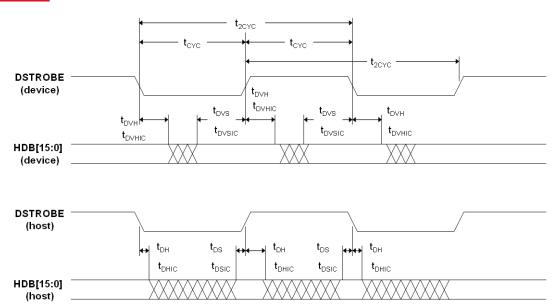

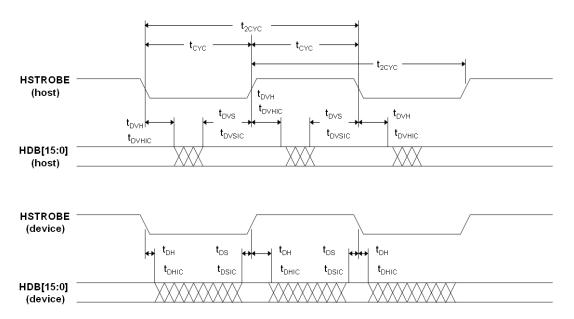

| FIGURE 11: ULTRA DMA MODE DATA-IN BURST INITIATION TIMING DIAGRAM        | 33 |

| FIGURE 12: ULTRA DMA MODE DATA-OUT BURST INITIATION TIMING DIAGRAM       | 33 |

| FIGURE 13: SUSTAINED ULTRA DMA MODE DATA-IN BURST TIMING DIAGRAM         | 34 |

| FIGURE 14: SUSTAINED ULTRA DMA MODE DATA-OUT BURST TIMING DIAGRAM        | 34 |

| FIGURE 15: TIMING DIAGRAM, HARDWARE RESET                                | 51 |

| FIGURE 16 TIMING DIAGRAM, POWER ON RESET                                 | 52 |

## 1. Product Overview

### 1.1 Introduction of Innodisk iCF 1SE

The Innodisk Industrial CompactFlash® 1SE Memory Card (iCF 1SE) products provide high capacity solid-state flash memory that electrically complies with the Personal Computer Memory Card International Association (PCMCIA) ATA (PC Card ATA) standard. (In Japan, the applicable standards group is JEIDA.) The CompactFlash® and PCMCIA cards support True IDE Mode that is electrically compatible with an IDE disk drive. The original CF form factor card can be used in any system that has a CF slot. Designed to replace traditional rotating disk drives, Innodisk Industrial CompactFlash® 1SE Memory Cards are embedded solid-state data storage systems for mobile computing and the industrial work place. The Industrial CompactFlash® features an extremely lightweight, reliable, low-profile form factor.

Industrial CompactFlash® 1SE (iCF 1SE) supports advanced PIO (0-6), Multiword DMA (0-2), Ultra DMA (0-4) transfer modes, multi-sector transfers, and LBA addressing.

### 1.2 Product View and Models

Innodisk iCF 1SE is available in follow capacities with industrial 3D TLC flash ICs.

Figure 1: Innodisk iCF 1SE

# 2. Product Specifications

The Industrial ATA products provide the following system features:

- Capacities: 512MB~8GB

- Fully compatible with CompactFlash® specification version 3.0

- · Fully compatible with PC Card Standard.

- Fully compatible with the IDE standard interface, ATA Standard

- · Three access modes

- PC Card Memory Mode

- PC Card I/O Mode

- True IDE Mode

- ECC (Error Correction Code) function: 4 bits/ per 512 byte

- +3.3V/+5V single power supply operation

- · Support Auto Stand-by and Sleep Mode.

- Power Consumption

|        |      | Active mode    |                 |                            |  |  |  |  |  |

|--------|------|----------------|-----------------|----------------------------|--|--|--|--|--|

|        |      | Read operation | Write operation | Power Down<br>mode         |  |  |  |  |  |

| Simala | 5V   | 69mA(Typ.)     | 59mA(Typ.)      | 1.2mA (Typ./max.)          |  |  |  |  |  |

| Single | 3.3V | 67mA(Typ.)     | 52mA(Typ.)      | 0.7mA (Typ./max.)          |  |  |  |  |  |

|        | 5V   | 115mA(Typ.)    | 100mA(Typ.)     | 1.7mA (Typ./max.)          |  |  |  |  |  |

| Dual   | 3.3V | 121mA(Typ.)    | 115mA(Typ.)     | 0.6mA (Typ.),<br>0.7(max.) |  |  |  |  |  |

• Support transfer modes: (0-4), Multiword DMA (0-2) and Ultra DMA(0-4)

• MTBF 3,000,000 hours

· Data retention: 10 years

• R/W performance:

|        | Capacity  | Read               | Write             |  |

|--------|-----------|--------------------|-------------------|--|

| Single | 512MB~2GB | 20 Mbytes/s. (MAX) | 10 Mbytes/s (MAX) |  |

| Dual   | 1GB~8GB   | 40 Mbytes/s. (MAX) | 30 Mbytes/s (MAX) |  |

· Operating temperature range:

- Standard Grade: 0°C ~ +70°C

- Industrial Grade: -40°C ~ +85°C

• Storage temperature range: -55°C ~ +95°C

# 3. Pin Assignment

See Table 1 for iCF 1SE pin assignments.

**Table 1: iCF 1SE Pin Assignments**

| PC Card Memory Mode |                   | PC Card I/O Mode |         |                   | True IDE Mode |         |                   |     |

|---------------------|-------------------|------------------|---------|-------------------|---------------|---------|-------------------|-----|

| Pin No.             | Name              | I/O              | Pin No. | Name              | I/O           | Pin No. | Name              | I/O |

| 1                   | GND               |                  | 1       | GND               |               | 1       | GND               |     |

| 2                   | D03               | I/O              | 2       | D03               | I/O           | 2       | D03               | I/O |

| 3                   | D04               | I/O              | 3       | D04               | I/O           | 3       | D04               | I/O |

| 4                   | D05               | I/O              | 4       | D05               | I/O           | 4       | D05               | I/O |

| 5                   | D06               | I/O              | 5       | D06               | I/O           | 5       | D06               | I/O |

| 6                   | D07               | I/O              | 6       | D07               | I/O           | 6       | D07               | I/O |

| 7                   | -CE1              | I                | 7       | -CE1              | I             | 7       | -CS0              | I   |

| 8                   | A10               | I                | 8       | A10               | I             | 8       | A10 <sup>2</sup>  | I   |

| 9                   | -OE               | I                | 9       | -OE               | I             | 9       | -ATA SEL          | I   |

| 10                  | A09               | I                | 10      | A09               | I             | 10      | A09 <sup>2</sup>  | I   |

| 11                  | A08               | I                | 11      | A08               | I             | 11      | A08 <sup>2</sup>  | I   |

| 12                  | A07               | I                | 12      | A07               | I             | 12      | A07 <sup>2</sup>  | I   |

| 13                  | VCC               |                  | 13      | VCC               |               | 13      | VCC               |     |

| 14                  | A06               | I                | 14      | A06               | I             | 14      | A06 <sup>2</sup>  | I   |

| 15                  | A05               | I                | 15      | A05               | I             | 15      | A05 <sup>2</sup>  | I   |

| 16                  | A04               | I                | 16      | A04               | I             | 16      | A04 <sup>2</sup>  | I   |

| 17                  | A03               | I                | 17      | A03               | I             | 17      | A03 <sup>2</sup>  | I   |

| 18                  | A02               | I                | 18      | A02               | I             | 18      | A02               | I   |

| 19                  | A01               | I                | 19      | A01               | I             | 19      | A01               | I   |

| 20                  | A00               | I                | 20      | A00               | I             | 20      | A00               | I   |

| 21                  | D00               | I/O              | 21      | D00               | I/O           | 21      | D00               | I/O |

| 22                  | D01               | I/O              | 22      | D01               | I/O           | 22      | D01               | I/O |

| 23                  | D02               | I/O              | 23      | D02               | I/O           | 23      | D02               | I/O |

| 24                  | WP                | 0                | 24      | -IOIS16           | 0             | 24      | -IOCS16           | 0   |

| 25                  | -CD2              | 0                | 25      | -CD2              | 0             | 25      | -CD2              | 0   |

| 26                  | -CD1              | 0                | 26      | -CD1              | 0             | 26      | -CD1              | 0   |

| 27                  | D11 <sup>1</sup>  | I/O              | 27      | D11 <sup>1</sup>  | I/O           | 27      | D11 <sup>1</sup>  | I/O |

| 28                  | D12 <sup>1</sup>  | I/O              | 28      | D12 <sup>1</sup>  | I/O           | 28      | D12 <sup>1</sup>  | I/O |

| 29                  | D13 <sup>1</sup>  | I/O              | 29      | D13 <sup>1</sup>  | I/O           | 29      | D13 <sup>1</sup>  | I/O |

| 30                  | D14 <sup>1</sup>  | I/O              | 30      | D14 <sup>1</sup>  | I/O           | 30      | D14 <sup>1</sup>  | I/O |

| 31                  | D15 <sup>1</sup>  | I/O              | 31      | D15 <sup>1</sup>  | I/O           | 31      | D15 <sup>1</sup>  | I/O |

| 32                  | -CE2 <sup>1</sup> | I                | 32      | -CE2 <sup>1</sup> | I             | 32      | -CS1 <sup>1</sup> | I   |

| 33                  | -VS1              | 0                | 33      | -VS1              | 0             | 33      | -VS1              | 0   |

|    |                    |     |    |                    |     |    | -IORD <sup>7</sup>    |     |

|----|--------------------|-----|----|--------------------|-----|----|-----------------------|-----|

| 34 | -IORD              | I   | 34 | -IORD              | I   | 34 | HSTROBE <sup>8</sup>  | I   |

|    |                    |     |    |                    |     |    | -HDMARDY <sup>9</sup> |     |

| 35 | -IOWR              | I   | 35 | -IOWR              | I   | 35 | -IOWR <sup>7</sup>    | I   |

| 33 | -10WK              | 1   | 33 | -10VVK             | 1   | 33 | STOP <sup>8, 9</sup>  | 1   |

| 36 | -WE                | I   | 36 | -WE                | I   | 36 | -WE <sup>3</sup>      | I   |

| 37 | READY              | 0   | 37 | -IREQ              | 0   | 37 | INTRQ                 | 0   |

| 38 | VCC                |     | 38 | VCC                |     | 38 | VCC                   |     |

| 39 | -CSEL <sup>5</sup> | I   | 39 | -CSEL <sup>5</sup> | I   | 39 | -CSEL                 | I   |

| 40 | -VS2               | 0   | 40 | -VS2               | 0   | 40 | -VS2                  | 0   |

| 41 | RESET              | I   | 41 | RESET              | I   | 41 | -RESET                | I   |

|    |                    |     |    |                    |     |    | IORDY <sup>1</sup>    |     |

| 42 | -WAIT              | 0   | 42 | -WAIT              | 0   | 42 | -DDMARDY <sup>8</sup> | 0   |

|    |                    |     |    |                    |     |    | DSTROBE9              |     |

| 43 | -INPACK            | 0   | 43 | -INPACK            | 0   | 43 | DMARQ                 | 0   |

| 44 | -REG               | I   | 44 | -REG               | I   | 44 | -DMACK <sup>6</sup>   | I   |

| 45 | BVD2               | 0   | 45 | -SPKR              | 0   | 45 | -DASP                 | I/O |

| 46 | BVD1               | 0   | 46 | -STSCHG            | 0   | 46 | -PDIAG                | I/O |

| 47 | D08 <sup>1</sup>   | I/O | 47 | D08 <sup>1</sup>   | I/O | 47 | D08 <sup>1</sup>      | I/O |

| 48 | D09 <sup>1</sup>   | I/O | 48 | D09 <sup>1</sup>   | I/O | 48 | D09 <sup>1</sup>      | I/O |

| 49 | D10 <sup>1</sup>   | I/O | 49 | D10 <sup>1</sup>   | I/O | 49 | D10 <sup>1</sup>      | I/O |

| 50 | GND                |     | 50 | GND                |     | 50 | GND                   |     |

### Note:

- 1) These signals are required only for 16 bit accesses and not required when installed in 8 bit systems. Devices should allow for 3-state signals not to consume current.

- 2) The signal should be grounded by the host.

- 3) The signal should be tied to VCC by the host.

- 4) The mode is optional for CF+ Cards, but required for CompactFlash® Storage Cards.

- 5) The -CSEL signal is ignored by the card in PC Card modes. However, because it is not pulled up on the card in these modes, it should not be left floating by the host in PC Card modes. In these modes, the pin should be connected by the host to PC Card A25 or grounded by the host.

- 6) If DMA operations are not used, the signal should be held high or tied to VCC by the host. For proper operation in older hosts: while DMA operations are not active, the card shall ignore this signal, including a floating condition

- 7) Signal usage in True IDE Mode except when Ultra DMA mode protocol is active.

- 8) Signal usage in True IDE Mode when Ultra DMA mode protocol DMA Write is active.

- 9) Signal usage in True IDE Mode when Ultra DMA mode protocol DMA Read is active.

# 4. Pin Description

Table 2: describes the pin descriptions for iCF 1SE

|                                          | Pin      |     |                           |                                                                                                                                                                                                                                                                                                                                                               |

|------------------------------------------|----------|-----|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.                                  | Name     | I/O | Mode                      | Description                                                                                                                                                                                                                                                                                                                                                   |

| 8,10,11,<br>12,14,15,16,17<br>,18 19, 20 | A10 - A0 | I   | PC Card<br>Memory<br>Mode | These address lines along with the -REG signal are used to select the following: The I/O port address registers within the CompactFlash® Storage Card or CF+ Card, the memory mapped port address registers within the CompactFlash® Storage Card or CF+ Card, a byte in the card's information structure and its configuration control and status registers. |

| 8,10,11,<br>12,14,1516,17,<br>1819, 20   | A10 - A0 |     | PC Card<br>I/O<br>Mode    | This signal is the same as the PC Card Memory Mode signal.                                                                                                                                                                                                                                                                                                    |

| 18,19,20                                 | A2 – A0  |     | True IDE<br>Mode          | In True IDE Mode, only A[2:0] are used to select the one of eight registers in the Task File, the remaining address lines should be grounded by the host.                                                                                                                                                                                                     |

|                                          | BVD1     |     | PC Card<br>Memory<br>Mode | This signal is asserted high, as BVD1 is not supported.                                                                                                                                                                                                                                                                                                       |

| 46                                       | -STSCHG  | I/O | PC Card<br>I/O<br>Mode    | This signal is asserted low to alert the host to changes in the READY and Write Protect states, while the I/O interface is configured. Its use is controlled by the Card configuration and Status Register.                                                                                                                                                   |

|                                          | -PDIAG   |     | True IDE<br>Mode          | In the True IDE Mode, this input / output is the Pass Diagnostic signal in the Master / Slave handshake protocol.                                                                                                                                                                                                                                             |

|                                          | BVD2     |     | PC Card<br>Memory<br>Mode | This signal is asserted high, as BVD2 is not supported.                                                                                                                                                                                                                                                                                                       |

| 45                                       | -SPKR    | I/O | PC Card<br>I/O<br>Mode    | This line is the Binary Audio output from the card. If the Card does not support the Binary Audio function, this line should be held negated.                                                                                                                                                                                                                 |

|                                          | -DASP    |     | True IDE<br>Mode          | In the True IDE Mode, this input/output is the Disk Active/Slave Present signal in the Master/Slave handshake protocol.                                                                                                                                                                                                                                       |

|                |               |     |                  | These Card Detect pins are connected to ground on     |

|----------------|---------------|-----|------------------|-------------------------------------------------------|

|                |               |     | PC Card          | the CompactFlash® Storage Card or CF+ Card. They      |

|                |               |     | Memory           | are used by the host to determine that the            |

|                |               |     | Mode             | CompactFlash® Storage Card or CF+ Card is fully       |

| 26.25          | -CD1,         |     |                  | inserted into its socket.                             |

| 26, 25         | -CD2          | 0   | PC Card          |                                                       |

|                |               |     | I/O              | This signal is the same for all modes.                |

|                |               |     | Mode             |                                                       |

|                |               |     | True IDE         | This signal is the same for all modes.                |

|                |               |     | Mode             | This signal is the same for all modes.                |

|                |               |     |                  | These input signals are used both to select the card  |

|                |               |     |                  | and to indicate to the card whether a byte or a word  |

|                |               |     | PC Card          | operation is being performedCE2 always accesses       |

|                | -CE1,         |     | Memory           | the odd byte of the wordCE1 accesses the even         |

|                | -CE2          |     | Mode             | byte or the Odd byte of the word depending on A0      |

|                |               |     |                  | and -CE2. A multiplexing scheme based on A0,          |

|                |               |     |                  | -CE1, -CE2 allows 8 bit hosts to access all data on   |

| _              | -CE1,<br>-CE2 |     |                  | D0-D7.                                                |

| 7, 32          |               | I   | PC Card          | This signal is the same as the PC Card Memory Mode    |

|                |               |     | I/O              | signal.                                               |

|                |               |     | Mode             | In the True IDE Mode, -CS0 is the chip select for the |

|                |               |     | True IDE<br>Mode | task file registers while -CS1 is used to select the  |

|                |               |     |                  | Alternate Status Register and the Device Control      |

|                | -CS0,         |     |                  | Register.                                             |

|                | -CS1          |     |                  | While -DMACK is asserted, -CS0 and -CS1 shall be      |

|                |               |     |                  | held negated and the width of the transfers shall be  |

|                |               |     |                  | 16 bits.                                              |

|                |               |     | PC Card          | This signal is not used for this mode, but should be  |

|                |               |     | Memory           | connected by the host to PC Card A25 or grounded      |

|                |               |     | Mode             | by the host.                                          |

|                |               |     | PC Card          | This signal is not used for this mode, but should be  |

|                |               |     | I/O              | connected by the host to PC Card A25 or grounded      |

| 39             | -CSEL         | I   | Mode             | by the host.                                          |

|                |               |     |                  | This internally pulled up signal is used to configure |

|                |               |     | True IDE         | this device as a Master or a Slave when configured in |

|                |               |     | Mode             | the True IDE Mode. When this pin is grounded, this    |

|                |               |     | моае             | device is configured as a Master. When the pin is     |

|                |               |     |                  | open, this device is configured as a Slave.           |

| 2,3,4,5,6,31,3 | D15 -         | I/O | PC Card          | These lines carry the Data, Commands and Status       |

| 0,29,28,27,49, | D00     |   | Memory   | information between the host and the controller.        |  |  |

|----------------|---------|---|----------|---------------------------------------------------------|--|--|

| 48,47,23,22,21 |         |   | Mode     | D00 is the LSB of the Even Byte of the Word. D08 is     |  |  |

|                |         |   |          | the LSB of the Odd Byte of the Word.                    |  |  |

|                |         |   |          | ,                                                       |  |  |

|                |         |   | PC Card  |                                                         |  |  |

|                |         |   | I/O      | This signal is the same as the PC Card Memory Mode      |  |  |

|                |         |   | Mode     | signal.                                                 |  |  |

|                |         |   |          | In True IDE Mode, all Task File operations occur in     |  |  |

|                |         |   | True IDE | byte mode on the low order bus D[7:0] while all data    |  |  |

|                |         |   | Mode     | transfers are 16 bit using D[15:0].                     |  |  |

|                |         |   | PC Card  | J. C.               |  |  |

|                |         |   | Memory   | Ground.                                                 |  |  |

|                |         |   | Mode     |                                                         |  |  |

|                |         |   | PC Card  |                                                         |  |  |

| 1, 50          | GND     | - | I/O      | This signal is the same for all modes.                  |  |  |

|                |         |   | Mode     | This signal is the same for all modes.                  |  |  |

|                |         |   | True IDE |                                                         |  |  |

|                |         |   | Mode     | This signal is the same for all modes.                  |  |  |

|                |         |   | PC Card  |                                                         |  |  |

|                | -INPACK |   | Memory   | This signal is not used in this mode.                   |  |  |

|                |         |   | Mode     | This signal is not used in this mode.                   |  |  |

|                |         |   | Mode     | The Input Acknowledge signal is asserted by the         |  |  |

|                |         |   |          | CompactFlash® Storage Card or CF+ Card when the         |  |  |

|                |         | 0 | PC Card  | card is selected and responding to an I/O read cycle    |  |  |

|                | -INPACK |   | I/O      | at the address that is on the address bus. This signal  |  |  |

|                |         |   | Mode     | is used by the host to control the enable of any input  |  |  |

|                |         |   | Mode     | data buffers between the CompactFlash® Storage          |  |  |

|                |         |   |          | Card or CF+ Card and the CPU.                           |  |  |

|                |         |   |          | This signal is a DMA Request that is used for DMA       |  |  |

| 43             |         |   |          | data transfers between host and device. It shall be     |  |  |

|                |         |   |          | asserted by the device when it is ready to transfer     |  |  |

|                |         |   |          | data to or from the host. For Multiword DMA             |  |  |

|                |         |   |          | transfers, the direction of data transfer is controlled |  |  |

|                |         |   | True IDE | by -IORD and -IOWR. This signal is used in a            |  |  |

|                | DMARQ   |   | Mode     | handshake manner with -DMACK, i.e., the device          |  |  |

|                |         |   | Houe     | shall wait until the host asserts -DMACK before         |  |  |

|                |         |   |          | negating DMARQ, and reasserting DMARQ if there is       |  |  |

|                |         |   |          | more data to transfer. DMARQ shall not be driven        |  |  |

|                |         |   |          | when the device is not selected. While a DMA            |  |  |

|                |         |   |          |                                                         |  |  |

|                |         |   |          | operation is in progress, -CS0 and -CS1 shall be        |  |  |

| · · |                          |   |                                                                                | l                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|--------------------------|---|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |                          |   |                                                                                | held negated and the width of the transfers shall be                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |                          |   |                                                                                | 16 bits. If there is no hardware support for DMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |                          |   |                                                                                | mode in the host, this output signal is not used and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |                          |   |                                                                                | should not be connected at the host. In this case,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |                          |   |                                                                                | the BIOS must report that DMA mode is not                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |                          |   |                                                                                | supported by the host so that device drivers will not                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |                          |   |                                                                                | attempt DMA mode. A host that does not support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     |                          |   |                                                                                | DMA mode and implements both PCMCIA and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |                          |   |                                                                                | True-IDE modes of operation need not alter the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     |                          |   |                                                                                | PCMCIA mode connections while in True-IDE mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     |                          |   |                                                                                | as long as this does not prevent proper operation in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |                          |   |                                                                                | any mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |                          |   | PC Card                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |                          |   | Memory                                                                         | This signal is not used in this mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |                          |   | Mode                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     | -IORD                    |   | DC Card                                                                        | This is an I/O Read strobe generated by the host.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     |                          |   | I/O<br>Mode                                                                    | This signal gates I/O data onto the bus from the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |                          | I |                                                                                | CompactFlash® Storage Card or CF+ Card when the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |                          |   |                                                                                | card is configured to use the I/O interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |