# **Approval Sheet**

| Customer             |                           |

|----------------------|---------------------------|

| Product Number       | M4US-4GMSJIRG-B           |

| Module speed         | PC4-2133                  |

| Pin                  | 288 pin                   |

| CI-tRCD-tRP          | 15-15-15                  |

| SDRAM Operating Temp | -40℃~85℃                  |

| Date                 | 31 <sup>st</sup> May 2017 |

The Total Solution For Industrial Flash Storage

### 1. Features

#### Key Parameter

| Industry     | Speed | ed Data Rate MT/s |       |       |       | tRP   | tRC   |  |

|--------------|-------|-------------------|-------|-------|-------|-------|-------|--|

| Nomenclature | Grade | CL=11             | CL=13 | CL=15 | (ns)  | (ns)  | (ns)  |  |

| PC4-2133     | R     | 1600              | 1866  | 2133  | 14.06 | 14.06 | 47.06 |  |

- JEDEC Standard 288-pin Dual In-Line Memory Module

- Intend for PC4-2133 applications

- Inputs and Outputs are SSTL-12 compatible

- VDD=VDDQ= 1.2 Volt (TYP)

- VPP=2.5 Volt (TYP)

- VDDSPD=2.2-3.6V

- Low-Power auto self-refresh (LPASR)

- SDRAMs have 16 internal banks for concurrent operation (4 Bank Group of 4 banks each)

- Normal and Dynamic On-Die Termination for data, strobe and mask signals.

- Data bus inversion (DBI) for data bus

- Fixed burst chop (BC) of 4 and burst length (BL) of 8 via the MRS

- Selectable BC4 or BL8 on-the fly (OTF)

- Golden Connector

- Fly-By topology

- Terminated control, command and address

bus

- Programmable /CAS Latency:

- 10,11,12,13,14,15,16,17

- Operation temperature (-40 $^{\circ}$ C ~85 $^{\circ}$ C )

- On-die VREFDQ generation and Calibration

- On-Board EEPROM

- RoHS and Halogen free (Section 13)

### 2. Environmental Requirements

iDIMM are intended for use in standard office environments that have limited capacity for heating and air conditioning.

| Symbol | Parameter                                                                                     | Rating             | Units          | Notes    |

|--------|-----------------------------------------------------------------------------------------------|--------------------|----------------|----------|

| Topr   | Operating Temperature (ambient)                                                               | -40 to +85         | °C             | 1        |

| Тѕтс   | Storage Temperature                                                                           | -50 to +100        | °C             |          |

| Hopr   | Operating Humidity (relative)                                                                 | 10 to 90           | %              |          |

| Нѕтс   | Storage Humidity (without condensation)                                                       | 5 to 95            | %              |          |

| PBAR   | Barometric Pressure (operating & storage)                                                     | 105 to 69          | K Pascal       | 1,2      |

| DDR4   | component maximum case temperature (Tcase) sha<br>DRAM component specification.<br>o 9850 ft. | all not exceed the | value specifie | d in the |

### 3. SDRAM Parameters by device density

| RTT_Nom Setting | Param                    | 4Gb                      | Units |    |

|-----------------|--------------------------|--------------------------|-------|----|

|                 | Average periodic refresh | -40°C≦Tcase≦85°C         | 7.8   | μs |

| tREFI           | interval                 | 85°C< <b>Tcase≦95</b> °C | 3.9   | μs |

# 4. Ordering Information

| DDR4 W/T UDIMM  |         |          |              |           |         |     |

|-----------------|---------|----------|--------------|-----------|---------|-----|

| Part Number     | Donsity | Speed    | DIMM         | Number of | Number  | ECC |

|                 | Density |          | Organization | DRAM      | of rank | ECC |

| M4US-4GMSJIRG-B | 4GB     | PC4-2133 | 512Mx64      | 8         | 1       | Ν   |

#### Pin Configurations (Front side/Back side) 5. DDR4 512Mx8 base UDIMM

| Pin              | Front               | Pin      | Back              | Pin | Front               | Pin | Back    | Pin | Front               | Pin | Back         | Pin | Front               | Pin | Back   |

|------------------|---------------------|----------|-------------------|-----|---------------------|-----|---------|-----|---------------------|-----|--------------|-----|---------------------|-----|--------|

| 1                | NC                  | 145      | NC                | 37  | VSS                 | 181 | DQ29    | 73  | VDD                 | 217 | VDD          | 109 | VSS                 | 253 | DQ41   |

| 2                | VSS                 | 146      | VREFCA            | 38  | DQ24                | 182 | VSS     | 74  | CK0_t               | 218 | CK1_t        | 110 | DM5_n/<br>DBI5_n,NC | 254 | VSS    |

| 3                | DQ4                 | 147      | VSS               | 39  | VSS                 | 183 | DQ25    | 75  | СК0_с               | 219 | CK1_c        | 111 | NC                  | 255 | DQS5_c |

| 4                | VSS                 | 148      | DQ5               | 40  | DM3_n/<br>DBI3_n,NC | 184 | VSS     | 76  | VDD                 | 220 | VDD          | 112 | VSS                 | 256 | DQS5_t |

| 5                | DQ0                 | 149      | VSS               | 41  | NC                  | 185 | DQS3_c  | 77  | VTT                 | 221 | VTT          | 113 | DQ46                | 257 | VSS    |

| 6                | VSS                 | 150      | DQ1               | 42  | VSS                 | 186 | DQS3_t  | 78  | EVENT_n,NF          | 222 | PARITY       | 114 | VSS                 | 258 | DQ47   |

| 7                | DM0_n_t/<br>DBI0_n  | 151      | VSS               | 43  | DQ30                | 187 | VSS     | 79  | AO                  | 223 | VDD          | 115 | DQ42                | 259 | VSS    |

| 8                | NC                  | 152      | DQS0_c            | 44  | VSS                 | 188 | DQ31    | 80  | VDD                 | 224 | BA1          | 116 | VSS                 | 260 | DQ43   |

| 9                | VSS                 | 153      | DQS0_t            | 45  | DQ26                | 189 | VSS     | 81  | BAO                 | 225 | A10/AP       | 117 | DQ52                | 261 | VSS    |

| 10               | DQ6                 | 154      | VSS               | 46  | VSS                 | 190 | DQ27    | 82  | RAS_n<br>/A16       | 226 | VDD          | 118 | VSS                 | 262 | DQ53   |

| 11               | VSS                 | 155      | DQ7               | 47  | CB4/NC              | 191 | VSS     | 83  | VDD                 | 227 | NC           | 119 | DQ48                | 263 | VSS    |

| 12               | DQ2                 | 156      | VSS               | 48  | VSS                 | 192 | CB5,NC  | 84  | CS0_n               | 228 | WE_n/<br>A14 | 120 | VSS                 | 264 | DQ49   |

| 13               | VSS                 | 157      | DQ3               | 49  | CB0/NC              | 193 | VSS     | 85  | VDD                 | 229 | VDD          | 121 | DM6_n/<br>DBI6_n    | 265 | VSS    |

| 14               | DQ12                | 158      | VSS               | 50  | VSS                 | 194 | CB1,NC  | 86  | CAS_n/<br>A15       | 230 | NC           | 122 | NC                  | 266 | DQS6_c |

| 15               | VSS                 | 159      | DQ13              | 51  | DM8_n/<br>DBI8_n.NC | 195 | VSS     | 87  | ODT0                | 231 | VDD          | 123 | VSS                 | 267 | DQS6_t |

| 16               | DQ8                 | 160      | VSS               | 52  | NC                  | 196 | DQS8_c  | 88  | VDD                 | 232 | A13          | 124 | DQ54                | 268 | VSS    |

| 17               | VSS                 | 161      | DQ9               | 53  | VSS                 | 197 | DQS8_t  | 89  | CS1_n               | 233 | VDD          | 125 | VSS                 | 269 | DQ55   |

| 18               | DMI_n/<br>DBI1_n,NC | 162      | VSS               | 54  | CB6<br>DBI8_n,NC    | 198 | VSS     | 90  | VDD                 | 234 | NC           | 126 | DQ50                | 270 | VSS    |

| 19               | NC                  | 163      | DQS1_c            | 55  | VSS                 | 199 | CB7,NC  | 91  | ODT1                | 235 | NC           | 127 | VSS                 | 271 | DQ51   |

| 20               | VSS                 | 164      | DQS1_t            | 56  | CB2/NC              | 200 | VSS     | 92  | VDD                 | 236 | VDD          | 128 | DQ60                | 272 | VSS    |

| 21               | DQ14                | 165      | VSS               | 57  | VSS                 | 201 | CB3,NC  | 93  | NC                  | 237 | NC           | 129 | VSS                 | 273 | DQ61   |

| 22               | VSS                 | 166      | DQ15              | 58  | RESET_n             | 202 | VSS     | 94  | VSS                 | 238 | SA2          | 130 | DQ56                | 274 | VSS    |

| 23               | DQ10                | 167      | VSS               | 59  | VDD                 | 203 | CKE1    | 95  | DQ36                | 239 | VSS          | 131 | VSS                 | 275 | DQ57   |

| 24               | VSS                 | 168      | DQ11              | 60  | CKE0                | 204 | VDD     | 96  | VSS                 | 240 | DQ37         | 132 | DM7_n/<br>DBI7_n,NC | 276 | VSS    |

| 25               | DQ20                | 169      | VSS               | 61  | VDD                 | 205 | NC      | 97  | DQ32                | 241 | VSS          | 133 | NC                  | 277 | DQS7_c |

| 26               | VSS                 | 170      | DQ21              | 62  | ACT_n               | 206 | VDD     | 98  | VSS                 | 242 | DQ33         | 134 | VSS                 | 278 | DQS7_t |

| 27               | DQ16                | 171      | VSS               | 63  | BG0                 | 207 | BG1     | 99  | DM4_n/<br>DBI4_n,NC | 243 | VSS          | 135 | DQ62                | 279 | VSS    |

| 28               | VSS                 | 172      | DQ17              | 64  | VDD                 | 208 | ALERT_n | 100 | NC                  | 244 | DQS4_c       | 136 | VSS                 | 280 | DQ63   |

| 29               | DM2_n/<br>DBI2_n,NC | 173      | VSS               | 65  | A12/BC_n            | 209 | VDD     | 101 | VSS                 | 245 | DQS4_t       | 137 | DQ58                | 281 | VSS    |

| 30               | NC                  | 174      | DQS2_c            | 66  | A9                  | 210 | A11     | 102 | DQ38                | 246 | VSS          | 138 | VSS                 | 282 | DQ59   |

| 31               | VSS                 | 175      | DQS2_t            | 67  | VDD                 | 211 | A7      | 103 | VSS                 | 247 | DQ39         | 139 | SA0                 | 283 | VSS    |

| 32               | DQ22                | 176      | VSS               | 68  | A8                  | 212 | VDD     | 104 | DQ34                | 248 | VSS          | 140 | SA1                 | 284 | VSSSPD |

| 33               | VSS                 | 177      | DQ23              | 69  | A6                  | 213 | A5      | 105 | VSS                 | 249 | DQ35         | 141 | SCL                 | 285 | SDA    |

| 34               | DQ18                | 178      | VSS               | 70  | VDD                 | 214 | A4      | 106 | DQ44                | 250 | VSS          | 142 | VPP                 | 286 | VPP    |

| 35               | VSS                 | 179      | DQ19              | 71  | A3                  | 215 | VDD     | 107 | VSS                 | 251 | DQ45         | 143 | VPP                 | 287 | VPP    |

| 36               | DQ28                | 180      | VSS               | 72  | A1                  | 216 | A2      | 108 | DQ40                | 252 | VSS          | 144 | NC                  | 288 | VPP    |

| Note:<br>1. NC = | No Connect, RFU     | = Reserv | ed for Future Use | ,   |                     |     |         |     |                     |     |              |     |                     |     |        |

Note: 1. NC = No Connect, RFU = Reserved for Future Use 2. Address A17 is only valid for 16 Gb x4 based SDRAMs. 3. RAS\_n is a multiplexed function with A15. 4. CAS\_n is a multiplexed function with A15. 5. VVE\_n is a multiplexed function with A14. 6. CBx is for ECC UDIMM only

## 6. Architecture

### Pin Definition

| Pin Name                               | Description                   | Pin Name                                                 | Description                                                          |

|----------------------------------------|-------------------------------|----------------------------------------------------------|----------------------------------------------------------------------|

| Ax                                     | SDRAM address bus             | SCL                                                      | Serial Clock for temperature sensor/SPD<br>EEPROM                    |

| A10/AP                                 | Auto-Precharge                | DQx, CBx                                                 | Data input/output and check bit<br>input/output:                     |

| A12/BC_n                               | Burst Chop                    | DM_n/ DBI_n/TDQS_t<br>(DMU_n, DBIU_n),<br>(DML_n/DBII_n) | Input data mask and data bus inversion:                              |

| ACT_n                                  | Command Input                 | SDA                                                      | Serial Data                                                          |

| BAx                                    | Bank Address Inputs           | DQS_t<br>DQS_c<br>DQSU_t<br>DQSU_c<br>DQSL_t<br>DQSL_c   | Data strobe:                                                         |

| BGx                                    | Bank Group Address Inputs     | ALERT_n                                                  | Alert output                                                         |

| C0, C1,C2<br>(RDIMM or LRDIMM<br>only) | Chip ID                       | EVENT_n                                                  | Temperature event                                                    |

| CKx_t<br>CKx_c                         | Clock                         | TDQS_t, TDQS_c<br>(x8 DRAM-based RDIMM<br>only)          | Termination data strobe:                                             |

| CKEx                                   | Clock enable                  | VDD                                                      | Module power supply: 1.20V (TYP)                                     |

| CSx_n                                  | Chip Select                   | VPP                                                      | DRAM activating power supply: 2.5V –<br>0.125V / +0.250V             |

| ODTx                                   | On-Die Termination            | VREFCA                                                   | Reference voltage for control, command,<br>and address pins          |

| Parity                                 | Parity of Command and Address | VSS                                                      | Ground                                                               |

| RAS_n/A16<br>CAS_n/A15<br>WE_n/A14     | Command Input                 | VIT                                                      | Power supply for termination of address, command, and control VDD/2. |

| RESET_n                                | Active LOW asynchronous reset | VDDSPD                                                   | Power supply used to power the I2C bus<br>for SPD.                   |

| SAx                                    | Serial address Input          | RFU                                                      | Reserved for future use.                                             |

| NF                                     | No function                   | NC                                                       | No Connect                                                           |

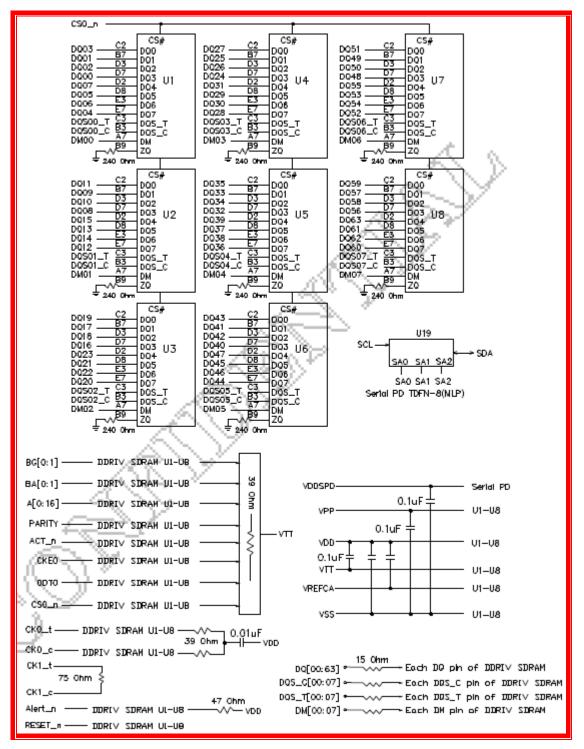

# 7. Function Block Diagram:

- (4GB, 1 Rank 512Mx8 DDR4 SDRAMs)

Note: 1. The ZQ ball on each DDR4 component is connected to an external  $240\Omega \pm 1\%$  resistor that is tied to ground. It is used for the calibration of the component's ODT and output driver.

| Symbol                            | Parameter                                         |                                       | Rating       | Units | Note |

|-----------------------------------|---------------------------------------------------|---------------------------------------|--------------|-------|------|

|                                   | Operation Temperature                             | Normal Operating Temp.                | -40 to 85    | °C    | 1,2  |

| T <sub>OPER</sub>                 | Operation Temperature<br>Extended Temp.(optional) |                                       | 85 to 95     | °C    | 1,3  |

| T <sub>STG</sub>                  | Storage Temperature                               |                                       | -55 to 100   | °C    | 4,5  |

| V <sub>IN,</sub> V <sub>OUT</sub> | Voltage on any pins rela                          | tive to Vss                           | -0.3 to +1.5 | V     | 4    |

| V <sub>DD</sub>                   | Voltage on VDD supply                             | Voltage on VDD supply relative to Vss |              | V     | 4,6  |

| V <sub>DDQ</sub>                  | Voltage on VDDQ supply relative to Vss            |                                       | -0.3 to +1.5 | V     | 4,6  |

### 8. SDRAM Absolute Maximum Ratings

#### Note:

1. Operating Temperature TOPER is the case surface temperature on the center / top side of the DRAM.

For measurement conditions, please refer to the JEDEC document JESD51-2.

The Normal Temperature Range specifies the temperatures where all DRAM specifications will be supported. During operation, the DRAM case temperature must be maintained between 0 to 85 °C under

all operating conditions.

3. Some applications require operation of the DRAM in the Extended Temperature Range between 85 °C and 95 °C case temperature. Full specifications are supported in this range, but the following additional

conditions apply:

a) Refresh commands must be doubled in frequency, therefore reducing the Refresh interval tREFI to 3.9 µs. It is also possible to specify a component with 1X refresh (tREFI to 7.8µs) in the Extended Temperature Range. Please refer to supplier data sheet and/or the DIMM SPD for option availability.

b) If Self-Refresh operation is required in the Extended Temperature Range, then it is mandatory to either use the Manual Self-Refresh mode with Extended Temperature Range capability (MR2 A6 =0b and MR2 A7 = 1b) or enable the optional Auto Self-Refresh mode (MR2 A6 = 1b and MR2 A7 =0b). Please refer to the supplier data sheet and/or the DIMM SPD for Auto Self-Refresh option availability, Extended Temperature Range support and tREFI requirements in the Extended Temperature Range.

4. Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is stress rating only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

5. Storage Temperature is the case surface temperature on the center/top side of the DRAM. For the measurement conditions, please refer to JESD51-2 standard.

6. VDD and VDDQ must be within 300 mV of each other at all times;and VREF must be not greater than 0.6 x VDDQ, When VDD and VDDQ are less than 500 mV; VREF may be equal to or less than 300 mV

## 9. Module Absolute Maximum Ratings

| Symbol                             | Parameter                              | Rating       | Units | Notes |

|------------------------------------|----------------------------------------|--------------|-------|-------|

| V <sub>IN</sub> , V <sub>OUT</sub> | Voltage on I/O pins relative to Vss    | -0.3 to +1.5 | V     |       |

| V <sub>DD</sub>                    | Voltage on VDD supply relative to Vss  | -0.3 to +1.5 | V     | 1     |

| V <sub>DDQ</sub>                   | Voltage on VDDQ supply relative to Vss | -0.3 to +1.5 | V     | 1     |

| V <sub>PP</sub>                    | Voltage on VPP supply relative to Vss  | -0.3 to +3.0 | V     | 2     |

| Note:                              |                                        |              |       |       |

Note:

1. VDDQ tracks with VDD; VDDQ and VDD are tied together.

2. VPP must be greater than or equal to VDD at all times.

### **10. Operating Condition**

innodisk

| Symbol            | Parameter                                                                                                | Min                  | Nom       | Max                  | Units | Notes |

|-------------------|----------------------------------------------------------------------------------------------------------|----------------------|-----------|----------------------|-------|-------|

| Vdd               | Supply Voltage                                                                                           | 1.14                 | 1.2       | 1.26                 | V     | 1     |

| VPP               | DRAM activating power supply                                                                             | 2.375                | 2.5       | 2.75                 | V     | 2     |

| VREFCA(DC)        | Input reference voltage command/<br>address bus                                                          | 0.49 x Vdd           | 0.5 x Vdd | 0.51 x Vdd           | V     | 3     |

| Ινττ              | Termination reference voltage<br>(DC) – command/address bus                                              | -750                 | -         | 750                  | mA    |       |

| VTT               | Termination Voltage                                                                                      | 0.49 × VDD -<br>20mV | 0.5 × VDD | 0.51 × VDD +<br>20mV | V     | 4     |

| h                 | Input leakage current; any input<br>excluding ZQ;<br>0V < VIN < 1.1V                                     | -2.0                 | -         | 2.0                  | μΑ    | 5     |

| II/O              | DQ leakage; 0V < Vin < VDD                                                                               | -4.0                 | -         | 4.0                  | μA    | 5     |

| loz <sub>pd</sub> | Output leakage current; VOUT =<br>VDD; DQ is disabled                                                    | -                    | -         | 5.0                  | μA    | 5,6   |

| lozpu             | Output leakage current; VOUT<br>=VSS; DQ and ODT are<br>disabled; ODT is disabled with<br>ODT input HIGH | Vref + 0.125         | -         | Vddq + 0.3           | μA    | 1     |

| loz <sub>pd</sub> | VREFCA leakage; VREFCA =<br>VDD/2 (after DRAM is initialized)                                            | -2.0                 | -         | 2.0                  | μA    | 5     |

Note:

1. VDDQ tracks with VDD; VDDQ and VDD are tied together.

2. VPP must be greater than or equal to VDD at all times.

3. VREFCA must not be greater than 0.6 x VDD. When VDD is less than 500mV, VREF may be less than or equal to 300mV.

4. VTT termination voltages in excess of the specification limit adversely affect the voltage margins of command and

address signals and reduce timing margins.

5. Multiply by the number of DRAM die on the module.

6. Tied to ground. Not connected to edge connector.

- 4GB UDIMM (1 Rank 512Mx8 DDR4 SDRAMs)

| Symbol | Drepood Conditions                                                                           | Va       | lue      | Units |

|--------|----------------------------------------------------------------------------------------------|----------|----------|-------|

| Symbol | Proposed Conditions                                                                          | IDD Max. | IPP Max. | Units |

|        | Operating One Bank Active-Precharge Current (AL=0)CKE: High; External clock: On; tCK,        |          |          |       |

| IDD0   | nRC, nRAS, CL: Refer to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n:         |          |          |       |

|        | Highbetween ACT and PRE; Command, Address, Bank Group Address, Bank Address                  |          |          |       |

|        | Inputs: partially toggling; Data IO: VDDQ; DM_n:stable at 1; Bank Activity: Cycling with one | 440      | 24       | mA    |

|        | bank active at a time: 0,0,1,1,2,2, ; Output Buffer and RTT: Enabled in Mode                 |          |          |       |

|        | Registers2;ODT Signal: stable at 0; Pattern Details: Refer to Component Datasheet for        |          |          |       |

|        | detail pattern                                                                               |          |          |       |

| IDD0A  | Operating One Bank Active-Precharge Current (AL=CL-1)                                        |          |          | ~ ^   |

| IDDUA  | AL = CL-1, Other conditions: see IDD0                                                        | -        | -        | mA    |

|        | Operating One Bank Active-Read-Precharge Current (AL=0)CKE: High;                            |          |          |       |

|        | External clock: On; tCK, nRC, nRAS, nRCD, CL: Refer to Component                             |          | -        |       |

|        | Datasheet for detail pattern; BL: 81; AL: 0; CS_n: Highbetween ACT, RD and                   |          |          |       |

| IDD1   | PRE; Command, Address, Bank Group Address, Bank Address Inputs, Data                         | 490      |          | ~^^   |

| וססו   | IO: partially toggling; DM_n: stableat 1; Bank Activity: Cycling with one bank               | 480      |          | mA    |

|        | active at a time: 0,0,1,1,2,2, ; Output Buffer and RTT: Enabled in Mode                      |          |          |       |

|        | Registers2; ODT Signal: stable at 0; Pattern Details: Refer to Component                     |          |          |       |

|        | Datasheet for detail pattern                                                                 |          |          |       |

|        | Operating One Bank Active-Read-Precharge Current (AL=CL-1)                                   |          |          |       |

| IDD1A  | AL = CL-1, Other conditions: see IDD1                                                        | -        | -        | mA    |

|        | Precharge Standby Current (AL=0)CKE: High; External clock: On; tCK, CL:                      |          |          |       |

|        | Refer to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n: stable at              |          |          |       |

|        | 1; Command,Address, Bank Group Address, Bank Address Inputs: partially                       | 220      |          |       |

| IDD2N  | toggling ; Data IO: VDDQ; DM_n: stable at 1; Bank Activity: all banksclosed;                 | 336      | -        | MA    |

|        | Output Buffer and RTT: Enabled in Mode Registers2; ODT Signal: stable at 0;                  |          |          |       |

|        | Pattern Details: Refer to Component Datasheet for detail pattern                             |          |          |       |

|        | Precharge Standby Current (AL=CL-1)                                                          |          |          |       |

| IDD2NA | AL = CL-1, Other conditions: see IDD2N                                                       | -        | -        | mA    |

|           | Precharge Standby ODT Current                                                 |     |     |     |

|-----------|-------------------------------------------------------------------------------|-----|-----|-----|

|           | CKE: High; External clock: On; tCK, CL: Refer to Component Datasheet for      |     |     |     |

|           | detail pattern; BL: 81; AL: 0; CS_n: stable at 1; Command, Address, Bank      |     |     |     |

| IDD2NT    | Group Address, Bank Address Inputs: partially toggling ; Data IO: VSSQ;       | 400 | -   | mA  |

|           | DM_n: stable at 1; Bank Activity: all banks closed; Output Buffer and RTT:    |     |     |     |

|           | Enabled in Mode Registers2; ODT Signal: toggling according ; Pattern Details: |     |     |     |

|           | Refer to Component Datasheet for detail pattern                               |     |     |     |

| IDD2NL    | Precharge Standby Current with CAL enabled                                    |     |     | mA  |

| IDDZINL   | Same definition like for IDD2N, CAL enabled3                                  | -   | -   | ША  |

|           | Precharge Standby Current with Gear Down mode enabled                         |     |     | ~^^ |

| IDD2NG    | Same definition like for IDD2N, Gear Down mode enabled3                       | -   | -   | mA  |

|           | Precharge Standby Current with DLL disabled                                   |     |     |     |

| IDD2ND    | Same definition like for IDD2N, DLL disabled3                                 | -   | -   | mA  |

|           | Precharge Standby Current with CA parity enabled                              |     |     |     |

| IDD2N_par | Same definition like for IDD2N, CA parity enabled3                            | -   | -   | mA  |

|           | Precharge Power-Down Current CKE: Low; External clock: On; tCK, CL: Refer     |     | -   |     |

|           | to Component Datasheet for detail pattern; BL: 81; AL:0; CS_n: stable at 1;   |     |     |     |

|           | Command, Address, Bank Group Address, Bank Address Inputs: stable at 0;       |     |     |     |

| IDD2P     | Data IO: VDDQ; DM_n: stable at 1;                                             | 216 |     | mA  |

|           | Bank Activity: all banks closed; Output Buffer and RTT: Enabled in Mode       |     |     |     |

|           | Registers2; ODT Signal: stable at 0                                           |     |     |     |

|           | Precharge Quiet Standby Current                                               |     |     |     |

|           | CKE: High; External clock: On; tCK, CL: Refer to Component Datasheet for      |     |     |     |

|           | detail pattern; BL: 81; AL: 0; CS_n: stable at 1; Command,                    |     |     |     |

| IDD2Q     | Address, Bank Group Address, Bank Address Inputs: stable at 0; Data IO:       | 280 | -   | mA  |

|           | VDDQ; DM_n: stable at 1;Bank Activity: all banks closed;                      |     |     |     |

|           | Output Buffer and RTT: Enabled in Mode Registers2; ODT Signal: stable at 0    |     |     |     |

|           | Active Standby Current                                                        |     |     |     |

|           | CKE: High; External clock: On; tCK, CL: Refer to Component Datasheet for      |     |     |     |

|           | detail pattern; BL: 81; AL: 0; CS_n: stable at 1; Command,                    |     |     |     |

|           | Address, Bank Group Address, Bank Address Inputs: partially toggling ; Data   |     | ~ . |     |

| IDD3N     | IO: VDDQ; DM_n: stable at 1;Bank Activity: all banks                          | 440 | 24  | mA  |

|           | open; Output Buffer and RTT: Enabled in Mode Registers2; ODT Signal: stable   |     |     |     |

|           | at 0; Pattern Details:Refer to Component Datasheet                            |     |     |     |

|           | for detail pattern                                                            |     |     |     |

|           |                                                                               |     |     |     |

| IDD3NA | Active Standby Current (AL=CL-1)                                                | -    | - | mA |

|--------|---------------------------------------------------------------------------------|------|---|----|

|        | AL = CL-1, Other conditions: see IDD3N                                          |      |   |    |

| IDD3P  | Active Power-Down Current                                                       |      | - | mA |

|        | CKE: Low; External clock: On; tCK, CL: sRefer to Component Datasheet for        |      |   |    |

|        | detail pattern; BL: 81; AL: 0; CS_n: stable at 1; Command,                      | 320  |   |    |

|        | Address, Bank Group Address, Bank Address Inputs: stable at 0; Data IO:         | 020  |   |    |

|        | VDDQ; DM_n: stable at 1; Bank Activity: all banks open;                         |      |   |    |

|        | Output Buffer and RTT: Enabled in Mode Registers2; ODT Signal: stable at 0      |      |   |    |

|        | Operating Burst Read Current                                                    |      |   |    |

|        | CKE: High; External clock: On; tCK, CL: Refer to Component Datasheet for        |      |   |    |

|        | detail pattern; BL: 82; AL: 0; CS_n: High between RD;                           |      |   |    |

|        | Command, Address, Bank Group Address, Bank Address Inputs: partially            |      |   |    |

|        | toggling ; Data IO: seamless read data burst with different                     | 1000 |   |    |

| IDD4R  | data between one burst and the next one according ; DM_n: stable at 1; Bank     | 1080 | - | mA |

|        | Activity: all banks open, RD commands cycling through                           |      |   |    |

|        | banks: 0,0,1,1,2,2,; Output Buffer and RTT: Enabled in Mode Registers2;         |      |   |    |

|        | ODT Signal: stable at 0; Pattern Details: Refer to                              |      |   |    |

|        | Component Datasheet for detail pattern                                          |      |   |    |

|        | Operating Burst Read Current (AL=CL-1)                                          |      |   |    |

| IDD4RA | AL = CL-1, Other conditions: see IDD4R                                          | -    | - | mA |

|        | Operating Burst Read Current with Read DBI                                      |      |   |    |

| IDD4RB | Read DBI enabled3, Other conditions: see IDD4R                                  | -    | - | mA |

|        | Operating Burst Write Current                                                   |      | - | mA |

|        | CKE: High; External clock: On; tCK, CL: Refer to Component Datasheet for        |      |   |    |

|        | detail pattern; BL: 81; AL: 0; CS_n: High between WR;                           |      |   |    |

|        | Command, Address, Bank Group Address, Bank Address Inputs: partially            |      |   |    |

|        | toggling ; Data IO: seamless write data burst with different                    | 1010 |   |    |

| IDD4W  | data between one burst and the next one ; DM_n: stable at 1; Bank Activity: all | 1240 |   |    |

|        | banks open, WR commands cycling through banks:                                  |      |   |    |

|        | 0,0,1,1,2,2,; Output Buffer and RTT: Enabled in Mode Registers2; ODT            |      |   |    |

|        | Signal: stable at HIGH; Pattern Details: Refer to Component                     |      |   |    |

|        | Datasheet for detail pattern                                                    |      |   |    |

|        | Operating Burst Write Current (AL=CL-1)                                         |      |   |    |

| IDD4WA | AL = CL-1, Other conditions: see IDD4W                                          | -    | - | mA |

|        | Operating Burst Write Current with Write DBI                                    |      |   |    |

| IDD4WB | Write DBI enabled3, Other conditions: see IDD4W                                 | -    | - | mA |

|        |                                                                                 | 1    | 1 |    |

|           | Operating Burst Write Current with Write CRC                                                                                                                                                 |      |     |     |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|

| IDD4WC    | Write CRC enabled3, Other conditions: see IDD4W                                                                                                                                              | -    | -   | mA  |

|           | Operating Burst Write Current with CA Parity                                                                                                                                                 |      |     | ~ ^ |

| IDD4W_par | CA Parity enabled3, Other conditions: see IDD4W                                                                                                                                              | -    | -   | mA  |

|           | Burst Refresh Current (1X REF)                                                                                                                                                               |      |     |     |

|           | CKE: High; External clock: On; tCK, CL, nRFC: Refer to Component Datasheet                                                                                                                   |      |     |     |

|           | for detail pattern; BL: 81; AL: 0; CS_n: High between                                                                                                                                        |      |     |     |

| IDD5B     | REF; Command, Address, Bank Group Address, Bank Address Inputs: partially                                                                                                                    |      | 176 |     |

| IDD3B     | toggling ; Data IO: VDDQ; DM_n: stable at 1; Bank                                                                                                                                            | 1360 | 176 | mA  |

|           | Activity: REF command every nRFC ; Output Buffer and RTT: Enabled in Mode                                                                                                                    |      |     |     |

|           | Registers2; ODT Signal: stable at 0; Pattern Details:                                                                                                                                        |      |     |     |

|           | Refer to Component Datasheet for detail pattern                                                                                                                                              |      |     |     |

|           | Burst Refresh Current (2X REF)                                                                                                                                                               |      |     |     |

| IDD5F2    | tRFC=tRFC_x2, Other conditions: see IDD5B                                                                                                                                                    | -    | -   | mA  |

|           |                                                                                                                                                                                              |      |     |     |

|           | Burst Refresh Current (4X REF)                                                                                                                                                               |      |     |     |

| IDD5F4    | tRFC=tRFC_x4, Other conditions: see IDD5B                                                                                                                                                    | -    | -   | mA  |

|           | Self Refresh Current: Normal Temperature Range                                                                                                                                               |      |     |     |

|           | TCASE: 0 - 85°C; Low Power Array Self Refresh (LP ASR) : Normal4; CKE:<br>Low; External clock: Off; CK_t and CK_c#: LOW; CL: Refer                                                           |      |     |     |

|           |                                                                                                                                                                                              |      |     |     |

| IDD6N     | to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n#, Command,                                                                                                                    | 144  | -   | mA  |

|           | Address, Bank Group Address, Bank Address, Data IO:                                                                                                                                          |      |     |     |

|           | High; DM_n: stable at 1; Bank Activity: Self-Refresh operation; Output Buffer                                                                                                                |      |     |     |

|           | and RTT: Enabled in Mode Registers2; ODT Signal: MIDLEVEL                                                                                                                                    |      |     |     |

|           | Self-Refresh Current: Extended Temperature Range)         TCASE: 0 - 95°C; Low Power Array Self Refresh (LP ASR) : Extended4; CKE:         Low; External clock: Off; CK_t and CK_c: LOW; CL: |      |     |     |

|           |                                                                                                                                                                                              |      |     |     |

|           |                                                                                                                                                                                              |      |     |     |

|           | Refer to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n,                                                                                                                        | 400  | -   | mA  |

| IDD6E     | Command, Address, Bank Group Address, Bank Address, Data                                                                                                                                     | 192  |     |     |

|           | IO: High; DM_n:stable at 1; Bank Activity: Extended Temperature Self-Refresh                                                                                                                 |      |     |     |

|           | operation; Output Buffer and RTT: Enabled in Mode                                                                                                                                            |      |     |     |

|           | Registers2; ODT Signal: MID-LEVEL                                                                                                                                                            |      |     |     |

|           |                                                                                                                                                                                              |      |     |     |

| IDD6R | Self-Refresh Current: Reduced Temperature Range<br>TCASE: 0 - TBD (~35-45)°C; Low Power Array Self Refresh (LP ASR) :<br>Reduced4; CKE: Low; External clock: Off; CK_t and CK_c#: LOW;<br>CL: Refer to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n#,<br>Command, Address, Bank Group Address, Bank Address,<br>Data IO: High; DM_n:stable at 1; Bank Activity: Extended Temperature | 96   | -  | mA |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----|----|

|       | Self-Refresh operation; Output Buffer and RTT: Enabled in Mode<br>Registers2; ODT Signal: MID-LEVEL                                                                                                                                                                                                                                                                                                 |      |    |    |

|       | Auto Self-Refresh Current                                                                                                                                                                                                                                                                                                                                                                           |      |    |    |

|       | TCASE: 0 - 95°C; Low Power Array Self Refresh (LP ASR) : Auto4;Partial Array                                                                                                                                                                                                                                                                                                                        |      |    |    |

|       | Self-Refresh (PASR): Full Array; CKE: Low; External                                                                                                                                                                                                                                                                                                                                                 |      |    |    |

|       | clock: Off; CK_t and CK_c#: LOW; CL: Refer to Component Datasheet for                                                                                                                                                                                                                                                                                                                               |      |    |    |

| IDD6A | detail pattern; BL: 81; AL: 0; CS_n#, Command, Address, Bank                                                                                                                                                                                                                                                                                                                                        | 144  | -  | mA |

|       | Group Address, Bank Address, Data IO: High; DM_n:stable at 1; Bank Activity:                                                                                                                                                                                                                                                                                                                        |      |    |    |

|       | Auto Self-Refresh operation; Output Buffer and RTT:                                                                                                                                                                                                                                                                                                                                                 |      |    |    |

|       | Enabled in Mode Registers2; ODT Signal: MID-LEVEL                                                                                                                                                                                                                                                                                                                                                   |      |    |    |

|       | Operating Bank Interleave Read Current                                                                                                                                                                                                                                                                                                                                                              |      |    |    |

|       | CKE: High; External clock: On; tCK, nRC, nRAS, nRCD, nRRD, nFAW, CL:                                                                                                                                                                                                                                                                                                                                |      | 96 | mA |

|       | Refer to Component Datasheet for detail pattern; BL: 81; AL:                                                                                                                                                                                                                                                                                                                                        |      |    |    |

|       | CL-1; CS_n: High between ACT and RDA; Command, Address, Bank Group                                                                                                                                                                                                                                                                                                                                  |      |    |    |

| IDD7  | Address, Bank Address Inputs: partially toggling ; DataIO: read data bursts with                                                                                                                                                                                                                                                                                                                    | 1320 |    |    |

| וססו  | different data between one burst and the next one ; DM_n: stable at 1; Bank                                                                                                                                                                                                                                                                                                                         | 1320 |    |    |

|       | Activity: two times interleaved cycling                                                                                                                                                                                                                                                                                                                                                             |      |    |    |

|       | through banks (0, 1,7) with different addressing; Output Buffer and RTT:                                                                                                                                                                                                                                                                                                                            |      |    |    |

|       | Enabled in Mode Registers2; ODT Signal: stable at 0; Pattern                                                                                                                                                                                                                                                                                                                                        |      |    |    |

|       | Details: Refer to Component Datasheet for detail pattern                                                                                                                                                                                                                                                                                                                                            |      |    |    |

| IDD8  | Maximum Power Down Current TBD                                                                                                                                                                                                                                                                                                                                                                      | 128  | -  | mA |

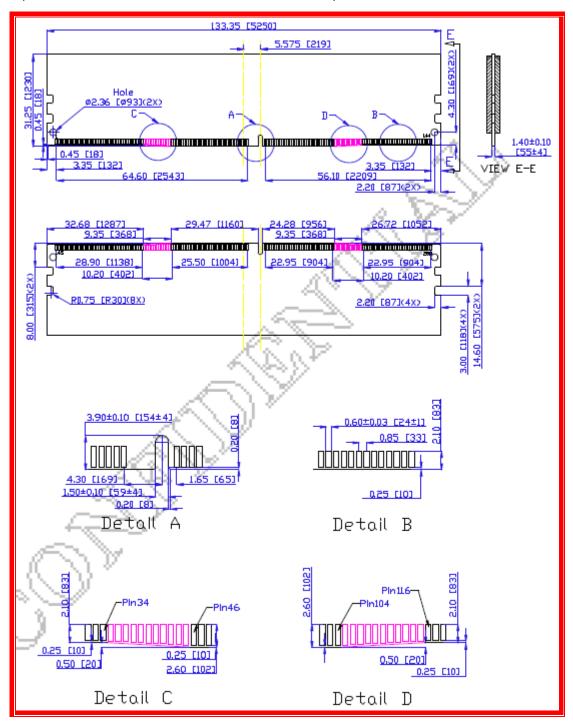

### **12. PACKAGE DIMENSION**

- (4GB, 1 Rank 512Mbx8 DDR4 base UDIMM)

Note: All dimensions are in millimeters (mils) and should be kept within a tolerance of  $\pm 0.15$  (6), unless otherwise specified.

# 13. RoHS Declaration

|     |                                                                       | <b>祭股份有限公司</b>                                                                    |  |

|-----|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------|--|

|     | Innodi                                                                | sk Corporation                                                                    |  |

|     |                                                                       | Tek(02)7703-3000 Fax:(02) 7703-3555 Internet: http://www.inmodisk.com             |  |

|     | RoHS自我宣告                                                              | (RoHS Declaration of Conformity)                                                  |  |

|     | Manufacturer Product: Al                                              | ll Innodisk EM Flash and Dram products                                            |  |

|     | 宜鼎國際股份有限公司(以下稱本公司)特此保證幣予費公司之所有產品,皆符合歐盟<br>2011/65/EU 關於 RoHS之規範要求。    |                                                                                   |  |

|     | Innodisk Corporation declares tha<br>European Union RoHS Directive (2 | at all products sold to the company, are complied wit<br>2011/65/EU) requirement. |  |

| = . | 本公司同意因本保證書或與本保證書                                                      | 相關事宜有所爭議時,雙方宜友好協商,達成協議。                                                           |  |

|     | Innodisk Corporation agrees that                                      | both parties shall settle any dispute arising fro                                 |  |

|     | or in connection with this Decla                                      | aration of Conformity by friendly negotiations.                                   |  |

|     | Name of hazardous substance                                           | Limited of RoHS ppm (mg/kg)                                                       |  |

|     | 鉛 (Pb)                                                                | < 1000 ppm                                                                        |  |

|     | 30 (TU)                                                               |                                                                                   |  |

|     | .≇ (Hα)                                                               | < 1000 ppm                                                                        |  |

|     | 汞 (Hg)<br>鍋 (Cd)                                                      | < 1000 ppm<br>< 100 ppm                                                           |  |

|     | 鍋 (Cd)                                                                | < 1000 ppm<br>< 100 ppm<br>< 1000 ppm                                             |  |

|     | 錦(Cd)<br>六價鉻(Cr 6+)                                                   | < 100 ppm                                                                         |  |

|     | 鍋 (Cd)                                                                | < 100 ppm<br>< 1000 ppm                                                           |  |

## **Revision Log**

| Rev | Date                      | Modification        |

|-----|---------------------------|---------------------|

| 0.1 | 31 <sup>st</sup> May 2017 | Preliminary Edition |

| 1.0 | 31 <sup>st</sup> May 2017 | Official Released   |