# **Approval Sheet**

| Customer                   |                                |

|----------------------------|--------------------------------|

| Product Number             | M4R0-BGS2BCEM                  |

| Module speed               | PC4-3200                       |

| Pin                        | 288 pin                        |

| CI-tRCD-tRP                | 22-22-22                       |

| Operation temperature (Tc) | 0℃~95℃                         |

| Date                       | 10 <sup>th</sup> November 2025 |

# The Total Solution For Industrial Flash Storage

### Features

# **Key Parameter**

| Industry     | Speed | Da    | ta Rate MT/ | 's    | CL | tRCD | tRP |

|--------------|-------|-------|-------------|-------|----|------|-----|

| Nomenclature | Grade | CL=19 | CL=21       | CL=22 | CL | IRCD | IRP |

| PC4-3200     | Е     | 2666  | 2933        | 3200  | 22 | 22   | 22  |

- JEDEC Standard 288-pin Registered Dual In-Line Memory Module

- Intend for PC4-3200 applications

- Inputs and Outputs are SSTL-12 compatible

- VDD=VDDQ= 1.2 Volt (1.14V~1.26V)

- VPP=2.5 Volt (2.375V~2.75V)

- VDDSPD=2.2-3.6V

- Low-Power auto self-refresh (LPASR)

- SDRAMs have 16 internal banks for concurrent operation (4 Bank Group of 4 banks each)

- Normal and Dynamic On-Die Termination for data, strobe and mask signals.

- Data bus inversion (DBI) for data bus

- Fixed burst chop (BC) of 4 and burst length (BL) of 8 via the MRS

- Selectable BC4 or BL8 on-the fly (OTF)

- Gold Plating Thickness 30µ"

- Fly-By topology

- Terminated control, command and address bus

- Programmable /CAS Latency:10,11,12,13,14,15,16,17,18,19,20,21,22,24

- On-die VREFDQ generation and Calibration

- Temperature Sensor with SPD EEPROM

- RoHS and Halogen free (Section 11)

- ECC Function

# 2. Ordering Information

| DDR4 RDIMM    |         |          |                      |                   |                   |      |     |

|---------------|---------|----------|----------------------|-------------------|-------------------|------|-----|

| Part Number   | Density | Speed    | DIMM<br>Organization | Number of<br>DRAM | Number<br>of rank | Side | ECC |

| M4R0-BGS2BCEM | 32GB    | PC4-3200 | 4Gx72                | 18                | 2                 | 2    | Y   |

# Pin Configurations (Front side/Back side)

## **DDR4 RDIMM**

| Pin | Front                | Pin | Back   | Pin | Front                 | Pin | Back    | Pin | Front                | Pin | Back           | Pin | Front                | Pin | Back  |

|-----|----------------------|-----|--------|-----|-----------------------|-----|---------|-----|----------------------|-----|----------------|-----|----------------------|-----|-------|

| 1   | NC                   | 145 | NC     | 37  | vss                   | 181 | DQ29    | 73  | VDD                  | 217 | VDD            | 109 | vss                  | 253 | DQ41  |

| 2   | VSS                  | 146 | VREFCA | 38  | DQ24                  | 182 | VSS     | 74  | CK0_t                | 218 | CK1_t          | 110 | DQS14_t/<br>TDQS14_t | 254 | VSS   |

| 3   | DQ4                  | 147 | VSS    | 39  | vss                   | 183 | DQ25    | 75  | CK0_c                | 219 | CK1_c          | 111 | DQS14_c/<br>TDQS14_c | 255 | DQS5_ |

| 4   | VSS                  | 148 | DQ5    | 40  | DQS12_t/<br>TDQS12_t  | 184 | VSS     | 76  | VDD                  | 220 | VDD            | 112 | VSS                  | 256 | DQS5_ |

| 5   | DQ0                  | 149 | VSS    | 41  | DQS12_c/<br>TDQS12_c  | 185 | DQS3_c  | 77  | VΠ                   | 221 | VTT            | 113 | DQ46                 | 257 | vss   |

| 6   | VSS                  | 150 | DQ1    | 42  | vss                   | 186 | DQS3_t  | 78  | EVENT_n              | 222 | PARITY         | 114 | vss                  | 258 | DQ47  |

| 7   | DQS9_t/<br>TDQS9_t   | 151 | VSS    | 43  | DQ30                  | 187 | VSS     | 79  | A0                   | 223 | VDD            | 115 | DQ42                 | 259 | VSS   |

| 8   | DQS09_c/<br>TDQS9_c  | 152 | DQS0_c | 44  | VSS                   | 188 | DQ31    | 80  | VDD                  | 224 | BA1            | 116 | VSS                  | 260 | DQ43  |

| 9   | VSS                  | 153 | DQS0_t | 45  | DQ26                  | 189 | VSS     | 81  | BA0                  | 225 | A10/AP         | 117 | DQ52                 | 261 | vss   |

| 10  | DQ6                  | 154 | VSS    | 46  | vss                   | 190 | DQ27    | 82  | RAS_n<br>/A16        | 226 | VDD            | 118 | vss                  | 262 | DQ53  |

| 11  | VSS                  | 155 | DQ7    | 47  | CB4                   | 191 | VSS     | 83  | VDD                  | 227 | RFU            | 119 | DQ48                 | 263 | VSS   |

| 12  | DQ2                  | 156 | VSS    | 48  | VSS                   | 192 | CB5     | 84  | CS0_n                | 228 | WE_n/<br>A14   | 120 | VSS                  | 264 | DQ49  |

| 13  | VSS                  | 157 | DQ3    | 49  | CB0                   | 193 | VSS     | 85  | VDD                  | 229 | VDD            | 121 | DQS15_t/<br>TDQS15_t | 265 | VSS   |

| 14  | DQ12                 | 158 | VSS    | 50  | vss                   | 194 | CB1     | 86  | CAS_n/<br>A15        | 230 | NC             | 122 | DQS15_c/<br>TDQS15_c | 266 | DQS6  |

| 15  | VSS                  | 159 | DQ13   | 51  | TDQS17_t/<br>TDQS17_t | 195 | VSS     | 87  | ODT0                 | 231 | VDD            | 123 | VSS                  | 267 | DQS6  |

| 16  | DQ8                  | 160 | VSS    | 52  | DQS17_c/<br>TDQS17_c  | 196 | DQS8_c  | 88  | VDD                  | 232 | A13            | 124 | DQ54                 | 268 | VSS   |

| 17  | VSS                  | 161 | DQ9    | 53  | vss                   | 197 | DQS8_t  | 89  | CS1_n                | 233 | VDD            | 125 | VSS                  | 269 | DQ5   |

| 18  | DQS10_t/<br>TDQS10_t | 162 | VSS    | 54  | CB6                   | 198 | VSS     | 90  | VDD                  | 234 | A17            | 126 | DQ50                 | 270 | vss   |

| 19  | DQS10_c/<br>TDQS10_c | 163 | DQS1_c | 55  | VSS                   | 199 | CB7     | 91  | ODT1                 | 235 | NC/C2          | 127 | VSS                  | 271 | DQ5   |

| 20  | VSS                  | 164 | DQS1_t | 56  | CB2                   | 200 | VSS     | 92  | VDD                  | 236 | VDD            | 128 | DQ60                 | 272 | VSS   |

| 21  | DQ14                 | 165 | vss    | 57  | vss                   | 201 | CB3     | 93  | CS2_n/C0,NC          | 237 | CS3_n<br>C1,NC | 129 | vss                  | 273 | DQ6   |

| 22  | VSS                  | 166 | DQ15   | 58  | RESET_n               | 202 | VSS     | 94  | VSS                  | 238 | SA2            | 130 | DQ56                 | 274 | VSS   |

| 23  | DQ10                 | 167 | VSS    | 59  | VDD                   | 203 | CKE1    | 95  | DQ36                 | 239 | VSS            | 131 | VSS                  | 275 | DQ57  |

| 24  | VSS                  | 168 | DQ11   | 60  | CKE0                  | 204 | VDD     | 96  | vss                  | 240 | DQ37           | 132 | DQS16_t/<br>TDQS16_t | 276 | vss   |

| 25  | DQ20                 | 169 | VSS    | 61  | VDD                   | 205 | RFU     | 97  | DQ32                 | 241 | VSS            | 133 | DQS16_c<br>/TDQS16_c | 277 | DQS7  |

| 26  | VSS                  | 170 | DQ21   | 62  | ACT_n                 | 206 | VDD     | 98  | vss                  | 242 | DQ33           | 134 | VSS                  | 278 | DQS7  |

| 27  | DQ16                 | 171 | VSS    | 63  | BG0                   | 207 | BG1     | 99  | DQS13_t/<br>TDQ13_t  | 243 | VSS            | 135 | DQ62                 | 279 | VSS   |

| 28  | VSS                  | 172 | DQ17   | 64  | VDD                   | 208 | ALERT_n | 100 | DQS13_c/<br>TDQS13_c | 244 | DQS4_c         | 136 | VSS                  | 280 | DQ63  |

| 29  | DQS11_t/<br>TDQS11_t | 173 | VSS    | 65  | A12/BC_n              | 209 | VDD     | 101 | VSS                  | 245 | DQS4_t         | 137 | DQ58                 | 281 | VSS   |

| 30  | DQS11_c/<br>TDQS11_c | 174 | DQS2_c | 66  | A9                    | 210 | A11     | 102 | DQ38                 | 246 | VSS            | 138 | VSS                  | 282 | DQ59  |

| 31  | VSS                  | 175 | DQS2_t | 67  | VDD                   | 211 | A7      | 103 | VSS                  | 247 | DQ39           | 139 | SA0                  | 283 | vss   |

| 32  | DQ22                 | 176 | VSS    | 68  | A8                    | 212 | VDD     | 104 | DQ34                 | 248 | VSS            | 140 | SA1                  | 284 | VDDSF |

| 33  | VSS                  | 177 | DQ23   | 69  | A6                    | 213 | A5      | 105 | VSS                  | 249 | DQ35           | 141 | SCL                  | 285 | SDA   |

| 34  | DQ18                 | 178 | VSS    | 70  | VDD                   | 214 | A4      | 106 | DQ44                 | 250 | VSS            | 142 | VPP                  | 286 | VPP   |

| 35  | VSS                  | 179 | DQ19   | 71  | А3                    | 215 | VDD     | 107 | VSS                  | 251 | DQ45           | 143 | VPP                  | 287 | VPP   |

| -   | DQ28                 | 180 | VSS    | 72  | A1                    | 216 | A2      | 108 | DQ40                 | 252 | VSS            | 144 | RFU                  | 288 | VPP   |

Address A17 is only valid for 16 Gb x4 bas

RAS\_n is a multiplexed function with A16.

CAS\_n is a multiplexed function with A15.

WE\_n is a multiplexed function with A14.

# 4. Architecture

### Pin Definition

| Pin Name                     | Description                                                      | Pin Name    | Description                                                    |

|------------------------------|------------------------------------------------------------------|-------------|----------------------------------------------------------------|

| A0-A17 <sup>1</sup>          | Register address input                                           | SCL         | I <sup>2</sup> C serial bus clock for SPD/TSE and register     |

| BAO, BA1                     | Register bank select input                                       | SDA         | I <sup>2</sup> C serial bus data line for SPD/TSE and register |

| BG0, BG1                     | Register bank group select input                                 | SA0-SA2     | I <sup>2</sup> C slave address select for SPD/TSE and registe  |

| RAS_n <sup>2</sup>           | Register row address strobe input                                | PAR         | Register parity input                                          |

| CAS_n <sup>3</sup>           | Register column address strobe input                             | VDD         | SDRAM core power supply                                        |

| WE_n <sup>4</sup>            | Register write enable input                                      | C0, C1,C2   | Chip ID lines for SDRAMs                                       |

| CSO_n, CS1_n<br>CS2_n, CS3_n | DIMM Rank Select Lines input                                     | 12 V        | Optional power Supply on socket but not used on RDIMM          |

| CKEO, CKE1                   | Register clock enable lines input                                | VREFCA      | SDRAM command/address reference supply                         |

| ODTO, ODT1                   | Register on-die termination control lines input                  | VSS         | Power supply return (ground)                                   |

| ACT_n                        | Register input for activate input                                | VDDSPD      | Serial SPD-TSE positive power supply                           |

| DQ0-DQ63                     | DIMM memory data bus                                             | ALERT_n     | Register ALERT_n output                                        |

| CBO-CB7                      | DIMM ECC check bits                                              | VPP         | SDRAM Supply                                                   |

| TDQS0_t-TDQS17_t             | Dummy loads formixed populations of x4                           |             |                                                                |

| TDQS0_c-TDQS17_c             | based and x8 based RDIMMs.                                       |             |                                                                |

| DQS0_t-DQS17_t               | Data Buffer data strobes<br>(positive line of differential pair) | DM0_n-DM8_n | Data Mask                                                      |

| DQS0_c-DQS17_c               | Data Buffer data strobes<br>(negative line of differential pair) | RESET_n     | Set Register and SDRAMs to a Known State                       |

| DBIO_n-DBI8_n                | Data Bus Inversion                                               | EVENT_n     | SPD signals a thermal event has occurred.                      |

| CK0_t, CK1_t                 | Register clock input (positive line of differential pair)        | VTT         | SDRAM I/O termination supply                                   |

| CK0_c, CK1_c                 | Register clocks input<br>(negative line of differential pair)    | RFU         | Reserved for future use                                        |

Note 1 Address A17 is only valid for 16 Gb x4 based SDRAMs.

Note 2 RAS\_n is a multiplexed function with A16.

Note 3 CAS\_n is a multiplexed function with A15.

Note 4 WE\_n is a multiplexed function with A14.

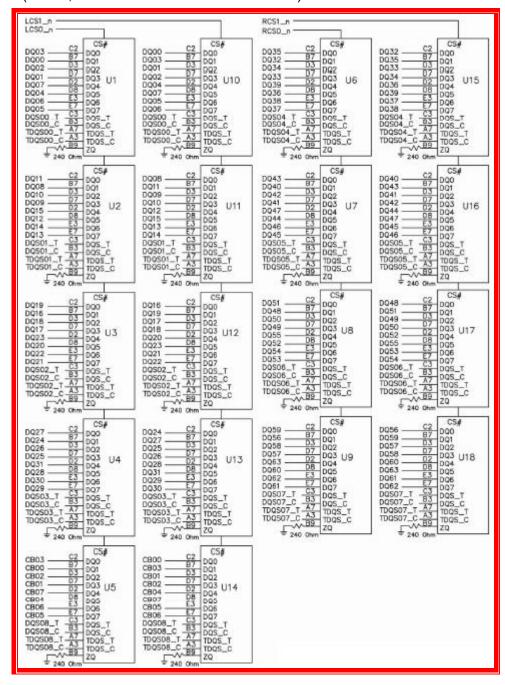

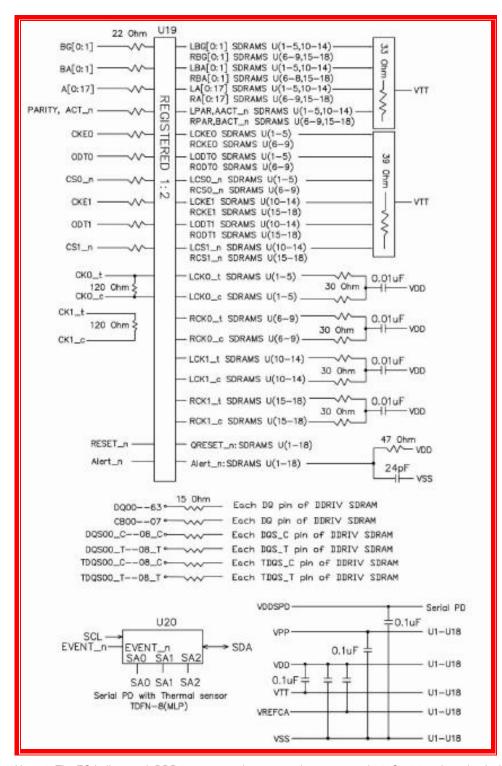

# 5. Function Block Diagram:

- (32GB, 2 Rank 2Gbx8 DDR4 SDRAMs)

Note: 1. The ZQ ball on each DDR4 component is connected to an external  $240\Omega \pm 1\%$  resistor that is tied to ground. It is used for the calibration of the component's ODT and output driver.

# 6. SDRAM Absolute Maximum Ratings

| Symbol                             | Pa                                   | arameter          | Rating       | Units | Note |

|------------------------------------|--------------------------------------|-------------------|--------------|-------|------|

| _                                  | On a resting Tanana and the          | Operating Temp.   | 0 to 85      | °C    | 1,2  |

| T <sub>OPER</sub>                  | Operation Temperature Extended Temp. |                   | 85 to 95     | °C    | 1,3  |

| T <sub>STG</sub>                   | Storage Temperature                  |                   | -55 to 100   | °C    | 4,5  |

| V <sub>IN</sub> , V <sub>OUT</sub> | Voltage on any pins rela             | tive to Vss       | -0.3 to +1.5 | V     | 4    |

| V <sub>DD</sub>                    | Voltage on VDD supply                | relative to Vss   | -0.3 to +1.5 | V     | 4,6  |

| V <sub>DDQ</sub>                   | Voltage on VDDQ suppl                | y relative to Vss | -0.3 to +1.5 | V     | 4,6  |

### Note

- 1) Operating Temperature TOPER is the case surface temperature on the center/top side of the DRAM.

- 2) The Normal Temperature Range specifies the temperatures where all DRAM specifications will be supported. During operation, the DRAM case temperature must be maintained between 0-85°C under all operating conditions.

- 3) Some applications require operation of the Extended Temperature Range between 85°C and 95°C case temperature. Full specifications are guaranteed in this range, but the following additional conditions apply:

- a) Refresh commands must be doubled in frequency, therefore reducing the refresh interval tREFI to 3.9us.

- b) If Self-Refresh operation is required in the Extended Temperature Range, then it is mandatory to either use the Manual Self-Refresh mode with Extended Temperature Range capability (MR2 A6 = 0b and MR2 A7 = 1b), in this case IDD6 current can be increased around 10~20% than normal Temperature range.

- 4. Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is stress rating only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- 5. Storage Temperature is the case surface temperature on the center/top side of the DRAM. For the measurement conditions, please refer to JESD51-2 standard.

- 6. VDD and VDDQ must be within 300 mV of each other at all times;and VREF must be not greater than 0.6 x VDDQ, When VDD and VDDQ are less than 500 mV; VREF may be equal to or less than 300 mV

# 7. Operating Condition

| Symbol     | Parameter                                       | Min        | Nom       | Max        | Units | Notes |

|------------|-------------------------------------------------|------------|-----------|------------|-------|-------|

| VDD        | Supply Voltage                                  | 1.14       | 1.2       | 1.26       | V     | 1     |

| VPP        | DRAM activating power supply                    | 2.375      | 2.5       | 2.75       | V     | 2     |

| VREFCA(DC) | Input reference voltage command/<br>address bus | 0.49 x VDD | 0.5 x VDD | 0.51 x VDD | V     | 3     |

| VTT        | Termination Voltage                             | 0.49 × VDD | 0.5 × VDD | 0.51 × VDD | V     | 4     |

### Note:

- 1. VDDQ tracks with VDD; VDDQ and VDD are tied together.

- VPP must be greater than or equal to VDD at all times.

- 3. VREFCA must not be greater than 0.6 x VDD. When VDD is less than 500mV, VREF may be less than or equal to 300mV.

- 4. VTT termination voltages in excess of the specification limit adversely affect the voltage margins of command and address signals and reduce timing margins.

# 8. Operating, Standby, and Refresh Currents

- 32GB RDIMM (2 Rank 2Gbx8 DDR4 SDRAMs)

| Comple of | Dranged Conditions                                                                           | Va       | lue      | Unito |

|-----------|----------------------------------------------------------------------------------------------|----------|----------|-------|

| Symbol    | Proposed Conditions                                                                          | IDD Max. | IPP Max. | Units |

|           | Operating One Bank Active-Precharge Current (AL=0)CKE: High; External clock: On; tCK,        |          |          |       |

|           | nRC, nRAS, CL: Refer to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n:         |          |          |       |

|           | Highbetween ACT and PRE; Command, Address, Bank Group Address, Bank Address                  |          |          |       |

| IDD0      | Inputs: partially toggling; Data IO: VDDQ; DM_n:stable at 1; Bank Activity: Cycling with one | 531      | 63       | mA    |

|           | bank active at a time: 0,0,1,1,2,2,; Output Buffer and RTT: Enabled in Mode                  |          |          |       |

|           | Registers2;ODT Signal: stable at 0; Pattern Details: Refer to Component Datasheet for        |          |          |       |

|           | detail pattern                                                                               |          |          |       |

| IDDOA     | Operating One Bank Active-Precharge Current (AL=CL-1)                                        | F 40     | 62       | Λ     |

| IDD0A     | AL = CL-1, Other conditions: see IDD0                                                        | 549      | 63       | mA    |

|           | Operating One Bank Active-Read-Precharge Current (AL=0)CKE: High;                            |          |          |       |

|           | External clock: On; tCK, nRC, nRAS, nRCD, CL: Refer to Component                             |          | 63       |       |

|           | Datasheet for detail pattern; BL: 81; AL: 0; CS_n: Highbetween ACT, RD and                   |          |          |       |

| 1004      | PRE; Command, Address, Bank Group Address, Bank Address Inputs, Data                         | 505      |          | •     |

| IDD1      | IO: partially toggling; DM_n: stableat 1; Bank Activity: Cycling with one bank               | 585      |          | mA    |

|           | active at a time: 0,0,1,1,2,2,; Output Buffer and RTT: Enabled in Mode                       |          |          |       |

|           | Registers2; ODT Signal: stable at 0; Pattern Details: Refer to Component                     |          |          |       |

|           | Datasheet for detail pattern                                                                 |          |          |       |

| .==       | Operating One Bank Active-Read-Precharge Current (AL=CL-1)                                   |          |          | _     |

| IDD1A     | AL = CL-1, Other conditions: see IDD1                                                        | 603      | 63       | mA    |

|           | Precharge Standby Current (AL=0)CKE: High; External clock: On; tCK, CL:                      |          |          |       |

|           | Refer to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n: stable at              |          |          |       |

|           | 1; Command,Address, Bank Group Address, Bank Address Inputs: partially                       |          |          | _     |

| IDD2N     | toggling; Data IO: VDDQ; DM_n: stable at 1; Bank Activity: all banksclosed;                  | 414      | 54       | mA    |

|           | Output Buffer and RTT: Enabled in Mode Registers2; ODT Signal: stable at 0;                  |          |          |       |

|           | Pattern Details: Refer to Component Datasheet for detail pattern                             |          |          |       |

|           | Precharge Standby Current (AL=CL-1)                                                          |          |          |       |

| IDD2NA    | AL = CL-1, Other conditions: see IDD2N                                                       | 414      | 54       | mA    |

|           |                                                                              |      | I          |    |

|-----------|------------------------------------------------------------------------------|------|------------|----|

|           | Precharge Standby ODT Current                                                |      |            |    |

|           | CKE: High; External clock: On; tCK, CL: Refer to Component Datasheet for     |      |            |    |

|           | detail pattern; BL: 81; AL: 0; CS_n: stable at 1; Command, Address, Bank     |      |            |    |

| IDD2NT    | Group Address, Bank Address Inputs: partially toggling; Data IO: VSSQ;       | 432  | 54         | mA |

|           | DM_n: stable at 1; Bank Activity: all banks closed; Output Buffer and RTT:   |      |            |    |

|           | Enabled in Mode Registers2; ODT Signal: toggling according; Pattern Details: |      |            |    |

|           | Refer to Component Datasheet for detail pattern                              |      |            |    |

| IDDONII   | Precharge Standby Current with CAL enabled                                   | 204  | F 4        | A  |

| IDD2NL    | Same definition like for IDD2N, CAL enabled3                                 | 324  | 54         | mA |

| IDDANIA   | Precharge Standby Current with Gear Down mode enabled                        | 44.4 | <b>5</b> 4 |    |

| IDD2NG    | Same definition like for IDD2N, Gear Down mode enabled3                      | 414  | 54         | mA |

|           | Precharge Standby Current with DLL disabled                                  |      |            | _  |

| IDD2ND    | Same definition like for IDD2N, DLL disabled3                                | 396  | 54         | mA |

|           | Precharge Standby Current with CA parity enabled                             |      |            | _  |

| IDD2N_par | Same definition like for IDD2N, CA parity enabled3                           | 450  | 54         | mA |

|           | Precharge Power-Down Current CKE: Low; External clock: On; tCK, CL: Refer    |      |            |    |

|           | to Component Datasheet for detail pattern; BL: 81; AL:0; CS_n: stable at 1;  |      | 54         |    |

|           | Command, Address, Bank Group Address, Bank Address Inputs: stable at 0;      | 306  |            |    |

| IDD2P     | Data IO: VDDQ; DM_n: stable at 1;                                            |      |            | mA |

|           | Bank Activity: all banks closed; Output Buffer and RTT: Enabled in Mode      |      |            |    |

|           | Registers2; ODT Signal: stable at 0                                          |      |            |    |

|           | Precharge Quiet Standby Current                                              |      |            |    |

|           | CKE: High; External clock: On; tCK, CL: Refer to Component Datasheet for     |      |            |    |

|           | detail pattern; BL: 81; AL: 0; CS_n: stable at 1; Command,                   |      |            | _  |

| IDD2Q     | Address, Bank Group Address, Bank Address Inputs: stable at 0; Data IO:      | 378  | 54         | mA |

|           | VDDQ; DM_n: stable at 1;Bank Activity: all banks closed;                     |      |            |    |

|           | Output Buffer and RTT: Enabled in Mode Registers2; ODT Signal: stable at 0   |      |            |    |

|           | Active Standby Current                                                       |      |            |    |

|           | CKE: High; External clock: On; tCK, CL: Refer to Component Datasheet for     |      |            |    |

|           | detail pattern; BL: 81; AL: 0; CS_n: stable at 1; Command,                   |      |            |    |

|           | Address, Bank Group Address, Bank Address Inputs: partially toggling; Data   |      |            | _  |

| IDD3N     | IO: VDDQ; DM_n: stable at 1;Bank Activity: all banks                         | 702  | 72         | mA |

|           | open; Output Buffer and RTT: Enabled in Mode Registers2; ODT Signal: stable  |      |            |    |

|           | at 0; Pattern Details:Refer to Component Datasheet                           |      |            |    |

|           | for detail pattern                                                           |      |            |    |

|           |                                                                              |      | <u> </u>   |    |

|         | Active Standby Current (AL=CL-1)                                               |      |    |       |

|---------|--------------------------------------------------------------------------------|------|----|-------|

| IDD3NA  | AL = CL-1, Other conditions: see IDD3N                                         | 720  | 72 | mA    |

|         | Active Power-Down Current                                                      |      |    |       |

|         | CKE: Low; External clock: On; tCK, CL: sRefer to Component Datasheet for       |      |    |       |

|         | detail pattern; BL: 81; AL: 0; CS_n: stable at 1; Command,                     |      |    |       |

| IDD3P   | Address, Bank Group Address, Bank Address Inputs: stable at 0; Data IO:        | 396  | 72 | mA    |

|         | VDDQ; DM_n: stable at 1; Bank Activity: all banks open;                        |      |    |       |

|         | Output Buffer and RTT: Enabled in Mode Registers2; ODT Signal: stable at 0     |      |    |       |

|         | Operating Burst Read Current                                                   |      |    |       |

|         | CKE: High; External clock: On; tCK, CL: Refer to Component Datasheet for       |      |    |       |

|         | detail pattern; BL: 82; AL: 0; CS_n: High between RD;                          |      |    |       |

|         | Command, Address, Bank Group Address, Bank Address Inputs: partially           |      |    |       |

|         | toggling; Data IO: seamless read data burst with different                     |      |    |       |

| IDD4R   | data between one burst and the next one according; DM_n: stable at 1; Bank     | 1359 | 72 | mA    |

|         | Activity: all banks open, RD commands cycling through                          |      |    |       |

|         | banks: 0,0,1,1,2,2,; Output Buffer and RTT: Enabled in Mode Registers2;        |      |    |       |

|         | ODT Signal: stable at 0; Pattern Details: Refer to                             |      |    |       |

|         | Component Datasheet for detail pattern                                         |      |    |       |

|         | Operating Burst Read Current (AL=CL-1)                                         |      |    |       |

| IDD4RA  | AL = CL-1, Other conditions: see IDD4R                                         | 1449 | 72 | mA    |

| 100.400 | Operating Burst Read Current with Read DBI                                     | 4000 | 70 | A     |

| IDD4RB  | Read DBI enabled3, Other conditions: see IDD4R                                 | 1863 | 72 | mA    |

|         | Operating Burst Write Current                                                  |      |    |       |

|         | CKE: High; External clock: On; tCK, CL: Refer to Component Datasheet for       |      |    |       |

|         | detail pattern; BL: 81; AL: 0; CS_n: High between WR;                          |      |    |       |

|         | Command, Address, Bank Group Address, Bank Address Inputs: partially           |      |    |       |

| IDD4W   | toggling ; Data IO: seamless write data burst with different                   | 1170 | 72 | mA    |

| 100444  | data between one burst and the next one; DM_n: stable at 1; Bank Activity: all | 1170 | 12 | IIIA  |

|         | banks open, WR commands cycling through banks:                                 |      |    |       |

|         | 0,0,1,1,2,2,; Output Buffer and RTT: Enabled in Mode Registers2; ODT           |      |    |       |

|         | Signal: stable at HIGH; Pattern Details: Refer to Component                    |      |    |       |

|         | Datasheet for detail pattern                                                   |      |    |       |

| IDD4WA  | Operating Burst Write Current (AL=CL-1)                                        | 1242 | 72 | mA    |

| IDD4VVA | AL = CL-1, Other conditions: see IDD4W                                         | 1242 | 12 | шл    |

| IDD4WB  | Operating Burst Write Current with Write DBI                                   | 1161 | 72 | mA    |

| 100400  | Write DBI enabled3, Other conditions: see IDD4W                                | 7101 | 12 | 111/1 |

| IDD4WC   Operating Burst Write Current with Write CRC write CRC enabled3, Other conditions: see IDD4W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | I <del></del>    |                                                                               | ı    | ı   | 1          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------|------|-----|------------|

| IDD4W_par   CA Parity enabled3, Other conditions: see IDD4W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IDD4WC           | Operating Burst Write Current with Write CRC                                  | 1089 | 72  | mA         |

| IDDSP  Burst Refresh Current (1X REF) CKE: High; External clock: On; tCK, CL, nRFC: Refer to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n: High between REF; Command, Address, Bank Group Address, Bank Address Inputs: partially toggling; Data IO: VDDQ; DM_n: stable at 1; Bank Address Inputs: partially toggling; Data IO: VDDQ; DM_n: stable at 1; Bank Address Inputs: partially toggling; Data IO: VDDQ; DM_n: stable at 1; Bank Address Inputs: partially toggling; Data IO: VDDQ; DM_n: stable at 1; Bank Address Inputs: partially toggling; Data IO: VDDQ; DM_n: stable at 0; Pattern Details: Refer to Component Datasheet for detail pattern  IDDSF2  Burst Refresh Current (2X REF) IRFC=IRFC_x2, Other conditions: see IDD5B  IDDSF4  Burst Refresh Current (4X REF) IRFC=tRFC_x4, Other conditions: see IDD5B  Self Refresh Current: Normal Temperature Range TCASE: 0 - 85°C; Low Power Array Self Refresh (LP ASR): Normal4; CKE: Low; External clock: Off; CK_t and CK_e#; LOW; CL: Refer  IDD6N  to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n#, Command, Address, Bank Group Address, Bank Address, Data IO: High; DM_n: stable at 1; Bank Activity: Self-Refresh operation; Output Buffer and RTT: Enabled in Mode Registers2; ODT Signal: MIDLEVEL  Self-Refresh Current: Extended Temperature Range) TCASE: 0 - 95°C; Low Power Array Self Refresh (LP ASR): Extended4; CKE: Low; External clock: Off; CK_t and CK_e: LOW; CL: Refer  Refer to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n, Command, Address, Bank Group Address, Bank Address, Bank Address, Data IO: High; DM_n:stable at 1; Bank Activity: Extended Temperature Self-Refresh operation; Output Buffer and RTT: Enabled in Mode |                  | Write CRC enabled3, Other conditions: see IDD4W                               |      |     |            |

| CA Parity enabled3, Other conditions: see IDD4W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | IDD4W par        | Operating Burst Write Current with CA Parity                                  | 1332 | 72  | mA         |

| CKE: High; External clock: On; tCK, CL, nRFC: Refer to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n: High between  REF; Command, Address, Bank Group Address, Bank Address Inputs: partially toggling; Data IO: VDDQ; DM_n: stable at 1; Bank  Activity: REF command every nRFC; Output Buffer and RTT: Enabled in Mode Registers2; ODT Signal: stable at 0; Pattern Details: Refer to Component Datasheet for detail pattern  IDD5F2  Burst Refresh Current (2X REF) tRFC=tRFC_x2, Other conditions: see IDD5B  IDD5F4  Burst Refresh Current (4X REF) tRFC=tRFC_x4, Other conditions: see IDD5B  Self Refresh Current: Normal Temperature Range TCASE: 0 - 85°C; Low Power Array Self Refresh (LP ASR): Normal4; CKE: Low; External clock: Off; CK_t and CK_c#; LOW; CL: Refer  IDD6N  IDD6N  Self-Refresh Current: Extended Temperature Range) TCASE: 0 - 95°C; Low Power Array Self Refresh operation; Output Buffer and RTT: Enabled in Mode Registers2; ODT Signal: MIDLEVEL  Self-Refresh Current: Extended Temperature Range) TCASE: 0 - 95°C; Low Power Array Self Refresh (LP ASR): Extended4; CKE: Low; External clock: Off; CK_t and CK_c#; LOW; CL: Refer to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n, Command, Address, Bank Corup Address, Bank Address, Data IO: Low; External clock: Off; CK_t and CK_c#; LOW; CL: Refer to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n, Command, Address, Bank Group Address, Bank Address, Data IO: High; DM_n: stable at 1; Bank Activity: Extended Temperature Self-Refresh operation; Output Buffer and RTT: Enabled in Mode                                                                                                                                       | .55 <u>_</u> pa. | CA Parity enabled3, Other conditions: see IDD4W                               | 1002 |     |            |

| for detail pattern; BL: 81; AL: 0; CS_n: High between  REF; Command, Address, Bank Group Address, Bank Address Inputs: partially toggling; Data IO: VDDQ; DM_n: stable at 1; Bank Activity: REF command every nRFC; Output Buffer and RTT: Enabled in Mode Registers2; ODT Signal: stable at 0; Pattern Details: Refer to Component Datasheet for detail pattern  IDD5F2  Burst Refresh Current (2X REF) tRFC=tRFC_x2, Other conditions: see IDD5B  IDD5F4  Burst Refresh Current (4X REF) tRFC=tRFC_x4, Other conditions: see IDD5B  Self Refresh Current: Normal Temperature Range TCASE: 0 - 85°C; Low Power Array Self Refresh (LP ASR): Normal4; CKE: Low; External clock: Off; CK_t and CK_c#: LOW; CL: Refer to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n#, Command, Address, Bank Group Address, Bank Address, Data IDD6B  IDD6B  IDD6B  Self-Refresh Current: Extended Temperature Range) TCASE: 0 - 95°C; Low Power Array Self Refresh operation; Output Buffer and RTT: Enabled in Mode Registers2; ODT Signal: MIDLEVEL  Self-Refresh Current: Extended Temperature Range) TCASE: 0 - 95°C; Low Power Array Self Refresh (LP ASR): Extended4; CKE: Low; External clock: Off; CK_t and CK_c: LOW; CL: Refer to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n, Command, Address, Bank Group Address, Bank Address, Data ID: High; DM_n: stable at 1; Bank Activity: Extended Temperature Self-Refresh operation; Output Buffer and RTT: Enabled in Mode Registers2; DT Signal: MIDLEVEL                                                                                                                                                                                                                                          |                  | Burst Refresh Current (1X REF)                                                |      |     |            |

| REF; Command, Address, Bank Group Address, Bank Address Inputs: partially toggling; Data IO: VDDQ; DM_n: stable at 1; Bank Activity: REF command every nRFC; Output Buffer and RTT: Enabled in Mode Registers2; ODT Signal: stable at 0; Pattern Details: Refer to Component Datasheet for detail pattern  IDD5F2  Burst Refresh Current (2X REF) tRFC=tRFC_x2, Other conditions: see IDD5B  Burst Refresh Current (4X REF) tRFC=tRFC_x4, Other conditions: see IDD5B  Self Refresh Current: Normal Temperature Range TCASE: 0 - 85°C; Low Power Array Self Refresh (LP ASR): Normal4; CKE: Low; External clock: Off; CK_t and CK_c#: LOW; CL: Refer to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n#, Command, Address, Bank Group Address, Bank Address, Data IDD6E  IDD6E  IDD6E  Self-Refresh Current: Extended Temperature Range) TCASE: 0 - 95°C; Low Power Array Self Refresh operation; Output Buffer and RTT: Enabled in Mode Registers2; ODT Signal: MIDLEVEL  Self-Refresh Current: Extended Temperature Range) TCASE: 0 - 95°C; Low Power Array Self Refresh (LP ASR): Extended4; CKE: Low; External clock: Off; CK_t and CK_c: LOW; CL: Refer to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n, Command, Address, Bank Group Address, Bank Address, Data ID: High; DM_n: stable at 1; Bank Activity: Extended Temperature Self-Refresh operation; Output Buffer and RTT: Enabled in Mode Registers2; DT Signal: MIDLEVEL                                                                                                                                                                                                                                                                                                         |                  | CKE: High; External clock: On; tCK, CL, nRFC: Refer to Component Datasheet    |      |     |            |

| toggling; Data IO: VDDQ; DM_n: stable at 1; Bank Activity: REF command every nRFC; Output Buffer and RTT: Enabled in Mode Registers2; ODT Signal: stable at 0; Pattern Details: Refer to Component Datasheet for detail pattern  IDD5F2 Burst Refresh Current (2X REF) tRFC=tRFC_x2, Other conditions: see IDD5B  IDD5F4 Burst Refresh Current (4X REF) tRFC=tRFC_x4, Other conditions: see IDD5B  Self Refresh Current: Normal Temperature Range TCASE: 0 - 85°C; Low Power Array Self Refresh (LP ASR): Normal4; CKE: Low; External clock: Off; CK_1 and CK_c#: LOW; CL: Refer  IDD6N to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n#, Command, Address, Bank Group Address, Bank Address, Data IO: High; DM_n: stable at 1; Bank Activity: Self-Refresh operation; Output Buffer and RTT: Enabled in Mode Registers2; ODT Signal: MIDLEVEL  Self-Refresh Current: Extended Temperature Range) TCASE: 0 - 95°C; Low Power Array Self Refresh (LP ASR): Extended4; CKE: Low; External clock: Off; CK_t and CK_c#. LOW; CL: Refer to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n, Command, Address, Bank Group Address, Bank Address, Data  IDD6E Refer to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n, Command, Address, Bank Group Address, Bank Address, Data IO: High; DM_n: stable at 1; Bank Activity: Extended Temperature Self-Refresh operation; Output Buffer and RTT: Enabled in Mode                                                                                                                                                                                                                                                                                                                           |                  | for detail pattern; BL: 81; AL: 0; CS_n: High between                         |      |     |            |

| toggling; Data IO: VDDQ; DM_n: stable at 1; Bank Activity: REF command every nRFC; Output Buffer and RTT: Enabled in Mode Registers2; ODT Signal: stable at 0; Pattern Details: Refer to Component Datasheet for detail pattern    IDD5F2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | IDD5R            | REF; Command, Address, Bank Group Address, Bank Address Inputs: partially     | 2997 | 567 | mΔ         |

| Registers2; ODT Signal: stable at 0; Pattern Details: Refer to Component Datasheet for detail pattern  Burst Refresh Current (2X REF) tRFC=tRFC_x2, Other conditions: see IDD5B  Burst Refresh Current (4X REF) tRFC=tRFC_x4, Other conditions: see IDD5B  Self Refresh Current: Normal Temperature Range TCASE: 0 - 85°C; Low Power Array Self Refresh (LP ASR): Normal4; CKE: Low; External clock: Off; CK_t and CK_c#: LOW; CL: Refer to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n#, Command, Address, Bank Group Address, Bank Address, Data IO: High; DM_n: stable at 1; Bank Activity: Self-Refresh operation; Output Buffer and RTT: Enabled in Mode Registers2; ODT Signal: MIDLEVEL  Self-Refresh Current: Extended Temperature Range) TCASE: 0 - 95°C; Low Power Array Self Refresh (LP ASR): Extended4; CKE: Low; External clock: Off; CK_t and CK_c: LOW; CL: Refer to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n, Command, Address, Bank Group Address, Bank Address, Data IO: High; DM_n:stable at 1; Bank Activity: Extended Temperature Self-Refresh operation; Output Buffer and RTT: Enabled in Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 10000            | toggling ; Data IO: VDDQ; DM_n: stable at 1; Bank                             | 2551 | 307 | ША         |

| Refer to Component Datasheet for detail pattern  Burst Refresh Current (2X REF) tRFC=tRFC_x2, Other conditions: see IDD5B  Burst Refresh Current (4X REF) tRFC=tRFC_x2, Other conditions: see IDD5B  Burst Refresh Current (4X REF) tRFC=tRFC_x4, Other conditions: see IDD5B  Self Refresh Current: Normal Temperature Range TCASE: 0 - 85°C; Low Power Array Self Refresh (LP ASR) : Normal4; CKE: Low; External clock: Off; CK_t and CK_c#: LOW; CL: Refer to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n#, Command, Address, Bank Group Address, Bank Address, Data IO: High; DM_n: stable at 1; Bank Activity: Self-Refresh operation; Output Buffer and RTT: Enabled in Mode Registers2; ODT Signal: MIDLEVEL  Self-Refresh Current: Extended Temperature Range) TCASE: 0 - 95°C; Low Power Array Self Refresh (LP ASR) : Extended4; CKE: Low; External clock: Off; CK_t and CK_c: LOW; CL: Refer to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n, Command, Address, Bank Group Address, Bank Address, Data IO: High; DM_n:stable at 1; Bank Activity: Extended Temperature Self-Refresh operation; Output Buffer and RTT: Enabled in Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  | Activity: REF command every nRFC ; Output Buffer and RTT: Enabled in Mode     |      |     |            |

| Burst Refresh Current (2X REF) tRFC=tRFC_x2, Other conditions: see IDD5B  Burst Refresh Current (4X REF) tRFC=tRFC_x4, Other conditions: see IDD5B  Self Refresh Current: Normal Temperature Range TCASE: 0 - 85°C; Low Power Array Self Refresh (LP ASR): Normal4; CKE: Low; External clock: Off; CK_t and CK_c#: LOW; CL: Refer to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n#, Command, Address, Bank Group Address, Bank Address, Data IO: High; DM_n: stable at 1; Bank Activity: Self-Refresh operation; Output Buffer and RTT: Enabled in Mode Registers2; ODT Signal: MIDLEVEL  Self-Refresh Current: Extended Temperature Range) TCASE: 0 - 95°C; Low Power Array Self Refresh (LP ASR): Extended4; CKE: Low; External clock: Off; CK_t and CK_c: LOW; CL: Refer to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n, Command, Address, Bank Group Address, Bank Address, Data IO: High; DM_n:stable at 1; Bank Activity: Extended Temperature Self-Refresh operation; Output Buffer and RTT: Enabled in Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                  | Registers2; ODT Signal: stable at 0; Pattern Details:                         |      |     |            |

| IDD5F2  IDD5F4  Burst Refresh Current (4X REF) tRFC=tRFC_x4, Other conditions: see IDD5B  Self Refresh Current: Normal Temperature Range TCASE: 0 - 85°C; Low Power Array Self Refresh (LP ASR): Normal4; CKE: Low; External clock: Off; CK_t and CK_c#: LOW; CL: Refer to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n#, Command, Address, Bank Group Address, Bank Address, Data IO: High; DM_n: stable at 1; Bank Activity: Self-Refresh operation; Output Buffer and RTT: Enabled in Mode Registers2; ODT Signal: MIDLEVEL  Self-Refresh Current: Extended Temperature Range) TCASE: 0 - 95°C; Low Power Array Self Refresh (LP ASR): Extended4; CKE: Low; External clock: Off; CK_t and CK_c: LOW; CL: Refer to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n, Command, Address, Bank Group Address, Bank Address, Data IO: High; DM_n:stable at 1; Bank Activity: Extended Temperature Self-Refresh operation; Output Buffer and RTT: Enabled in Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                  | Refer to Component Datasheet for detail pattern                               |      |     |            |

| IDD5F2  IDD5F4  Burst Refresh Current (4X REF) tRFC=tRFC_x4, Other conditions: see IDD5B  Self Refresh Current: Normal Temperature Range TCASE: 0 - 85°C; Low Power Array Self Refresh (LP ASR): Normal4; CKE: Low; External clock: Off; CK_t and CK_c#: LOW; CL: Refer to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n#, Command, Address, Bank Group Address, Bank Address, Data IO: High; DM_n: stable at 1; Bank Activity: Self-Refresh operation; Output Buffer and RTT: Enabled in Mode Registers2; ODT Signal: MIDLEVEL  Self-Refresh Current: Extended Temperature Range) TCASE: 0 - 95°C; Low Power Array Self Refresh (LP ASR): Extended4; CKE: Low; External clock: Off; CK_t and CK_c: LOW; CL: Refer to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n, Command, Address, Bank Group Address, Bank Address, Data IO: High; DM_n:stable at 1; Bank Activity: Extended Temperature Self-Refresh operation; Output Buffer and RTT: Enabled in Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                  | Burst Refresh Current (2X REF)                                                |      |     |            |

| IDD5F4  tRFC=tRFC_x4, Other conditions: see IDD5B  Self Refresh Current: Normal Temperature Range TCASE: 0 - 85°C; Low Power Array Self Refresh (LP ASR) : Normal4; CKE: Low; External clock: Off; CK_t and CK_c#: LOW; CL: Refer  to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n#, Command, Address, Bank Group Address, Bank Address, Data IO: High; DM_n: stable at 1; Bank Activity: Self-Refresh operation; Output Buffer and RTT: Enabled in Mode Registers2; ODT Signal: MIDLEVEL  Self-Refresh Current: Extended Temperature Range) TCASE: 0 - 95°C; Low Power Array Self Refresh (LP ASR) : Extended4; CKE: Low; External clock: Off; CK_t and CK_c: LOW; CL: Refer to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n, Command, Address, Bank Group Address, Bank Address, Data IO: High; DM_n:stable at 1; Bank Activity: Extended Temperature Self-Refresh operation; Output Buffer and RTT: Enabled in Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | IDD5F2           | · · ·                                                                         | 2277 | 387 | mA         |

| IDD5F4  tRFC=tRFC_x4, Other conditions: see IDD5B  Self Refresh Current: Normal Temperature Range TCASE: 0 - 85°C; Low Power Array Self Refresh (LP ASR) : Normal4; CKE: Low; External clock: Off; CK_t and CK_c#: LOW; CL: Refer  to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n#, Command, Address, Bank Group Address, Bank Address, Data IO: High; DM_n: stable at 1; Bank Activity: Self-Refresh operation; Output Buffer and RTT: Enabled in Mode Registers2; ODT Signal: MIDLEVEL  Self-Refresh Current: Extended Temperature Range) TCASE: 0 - 95°C; Low Power Array Self Refresh (LP ASR) : Extended4; CKE: Low; External clock: Off; CK_t and CK_c: LOW; CL: Refer to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n, Command, Address, Bank Group Address, Bank Address, Data IO: High; DM_n:stable at 1; Bank Activity: Extended Temperature Self-Refresh operation; Output Buffer and RTT: Enabled in Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                  |                                                                               |      |     |            |

| Self Refresh Current: Normal Temperature Range  TCASE: 0 - 85°C; Low Power Array Self Refresh (LP ASR): Normal4; CKE: Low; External clock: Off; CK_t and CK_c#: LOW; CL: Refer  to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n#, Command, Address, Bank Group Address, Bank Address, Data IO: High; DM_n: stable at 1; Bank Activity: Self-Refresh operation; Output Buffer and RTT: Enabled in Mode Registers2; ODT Signal: MIDLEVEL  Self-Refresh Current: Extended Temperature Range) TCASE: 0 - 95°C; Low Power Array Self Refresh (LP ASR): Extended4; CKE: Low; External clock: Off; CK_t and CK_c: LOW; CL: Refer to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n, Command, Address, Bank Group Address, Bank Address, Data IO: High; DM_n:stable at 1; Bank Activity: Extended Temperature Self-Refresh operation; Output Buffer and RTT: Enabled in Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | IDD5E4           | Burst Refresh Current (4X REF)                                                | 1827 | 324 | mΛ         |

| TCASE: 0 - 85°C; Low Power Array Self Refresh (LP ASR) : Normal4; CKE: Low; External clock: Off; CK_t and CK_c#: LOW; CL: Refer  to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n#, Command, Address, Bank Group Address, Bank Address, Data IO: High; DM_n: stable at 1; Bank Activity: Self-Refresh operation; Output Buffer and RTT: Enabled in Mode Registers2; ODT Signal: MIDLEVEL  Self-Refresh Current: Extended Temperature Range) TCASE: 0 - 95°C; Low Power Array Self Refresh (LP ASR) : Extended4; CKE: Low; External clock: Off; CK_t and CK_c: LOW; CL: Refer to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n, Command, Address, Bank Group Address, Bank Address, Data IO: High; DM_n:stable at 1; Bank Activity: Extended Temperature Self-Refresh operation; Output Buffer and RTT: Enabled in Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 100314           | tRFC=tRFC_x4, Other conditions: see IDD5B                                     | 1021 | 324 | ША         |

| Low; External clock: Off; CK_t and CK_c#: LOW; CL: Refer  to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n#, Command, Address, Bank Group Address, Bank Address, Data IO: High; DM_n: stable at 1; Bank Activity: Self-Refresh operation; Output Buffer and RTT: Enabled in Mode Registers2; ODT Signal: MIDLEVEL  Self-Refresh Current: Extended Temperature Range) TCASE: 0 - 95°C; Low Power Array Self Refresh (LP ASR): Extended4; CKE: Low; External clock: Off; CK_t and CK_c: LOW; CL: Refer to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n, Command, Address, Bank Group Address, Bank Address, Data IO: High; DM_n:stable at 1; Bank Activity: Extended Temperature Self-Refresh operation; Output Buffer and RTT: Enabled in Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                  | Self Refresh Current: Normal Temperature Range                                |      |     |            |

| IDD6N to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n#, Command, Address, Bank Group Address, Bank Address, Data IO: High; DM_n: stable at 1; Bank Activity: Self-Refresh operation; Output Buffer and RTT: Enabled in Mode Registers2; ODT Signal: MIDLEVEL  Self-Refresh Current: Extended Temperature Range) TCASE: 0 - 95°C; Low Power Array Self Refresh (LP ASR): Extended4; CKE: Low; External clock: Off; CK_t and CK_c: LOW; CL: Refer to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n, Command, Address, Bank Group Address, Bank Address, Data IO: High; DM_n:stable at 1; Bank Activity: Extended Temperature Self-Refresh operation; Output Buffer and RTT: Enabled in Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                  | TCASE: 0 - 85°C; Low Power Array Self Refresh (LP ASR) : Normal4; CKE:        |      |     |            |

| Address, Bank Group Address, Bank Address, Data IO: High; DM_n: stable at 1; Bank Activity: Self-Refresh operation; Output Buffer and RTT: Enabled in Mode Registers2; ODT Signal: MIDLEVEL  Self-Refresh Current: Extended Temperature Range) TCASE: 0 - 95°C; Low Power Array Self Refresh (LP ASR): Extended4; CKE: Low; External clock: Off; CK_t and CK_c: LOW; CL: Refer to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n, Command, Address, Bank Group Address, Bank Address, Data IO: High; DM_n:stable at 1; Bank Activity: Extended Temperature Self-Refresh operation; Output Buffer and RTT: Enabled in Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                  | Low; External clock: Off; CK_t and CK_c#: LOW; CL: Refer                      |      |     |            |

| High; DM_n: stable at 1; Bank Activity: Self-Refresh operation; Output Buffer and RTT: Enabled in Mode Registers2; ODT Signal: MIDLEVEL  Self-Refresh Current: Extended Temperature Range) TCASE: 0 - 95°C; Low Power Array Self Refresh (LP ASR): Extended4; CKE: Low; External clock: Off; CK_t and CK_c: LOW; CL: Refer to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n, Command, Address, Bank Group Address, Bank Address, Data IO: High; DM_n:stable at 1; Bank Activity: Extended Temperature Self-Refresh operation; Output Buffer and RTT: Enabled in Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | IDD6N            | to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n#, Command,     | 702  | 108 | mA         |

| and RTT: Enabled in Mode Registers2; ODT Signal: MIDLEVEL  Self-Refresh Current: Extended Temperature Range)  TCASE: 0 - 95°C; Low Power Array Self Refresh (LP ASR): Extended4; CKE: Low; External clock: Off; CK_t and CK_c: LOW; CL:  Refer to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n, Command, Address, Bank Group Address, Bank Address, Data  IO: High; DM_n:stable at 1; Bank Activity: Extended Temperature Self-Refresh operation; Output Buffer and RTT: Enabled in Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  | Address, Bank Group Address, Bank Address, Data IO:                           |      |     |            |

| Self-Refresh Current: Extended Temperature Range)  TCASE: 0 - 95°C; Low Power Array Self Refresh (LP ASR): Extended4; CKE:  Low; External clock: Off; CK_t and CK_c: LOW; CL:  Refer to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n,  Command, Address, Bank Group Address, Bank Address, Data  IO: High; DM_n:stable at 1; Bank Activity: Extended Temperature Self-Refresh operation; Output Buffer and RTT: Enabled in Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                  | High; DM_n: stable at 1; Bank Activity: Self-Refresh operation; Output Buffer |      |     |            |

| TCASE: 0 - 95°C; Low Power Array Self Refresh (LP ASR): Extended4; CKE:  Low; External clock: Off; CK_t and CK_c: LOW; CL:  Refer to Component Datasheet for detail pattern; BL: 81; AL: 0; CS_n,  Command, Address, Bank Group Address, Bank Address, Data  IO: High; DM_n:stable at 1; Bank Activity: Extended Temperature Self-Refresh operation; Output Buffer and RTT: Enabled in Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  | and RTT: Enabled in Mode Registers2; ODT Signal: MIDLEVEL                     |      |     |            |