# Approval Sheet

| Customer       |                                |

|----------------|--------------------------------|

| Product Number | M2SK-2GMF6IJ5-M                |

| Module speed   | PC2-5300                       |

| Pin            | 200 Pin                        |

| CL-tRCD-tRP    | 5-5-5                          |

| Operating Temp | -40°C ~ 85°C                   |

| Date           | 26 <sup>th</sup> February 2018 |

# The Total Solution For Industrial Flash Storage

#### 1. Features

**Key Parameter**

| Industry     | D    | ata Rate MT/s | S    | tRCD | tRP  | tRC  |

|--------------|------|---------------|------|------|------|------|

| Nomenclature | CL=3 | CL=4          | CL=5 | (ns) | (ns) | (ns) |

| PC2-5300     | 400  | 533           | 667  | 15   | 15   | 60   |

- JEDEC Standard 200-pin Small Outline Dual In-Line Memory Module

- Intend for 333MHz applications

- Inputs and Outputs are SSTL-18 compatible

- VDD=VDDQ= 1.8 Volt  $\pm$  0.1

- · Differential clock input

- All inputs are sampled at the positive going edge of the system clock

- Bi-Directional data strobe with one clock cycle preamble and one-half clock post-amble

- Address and control signals are fully synchronous to positive clock edge.

- Auto Refresh (CBR) and Self Refresh Modes support.

- Serial Presence Detect with EEPROM

- Automatic and controlled precharge commands.

- 14/10/2 Addressing (row/column/rank)-2GB

- Auto & self refresh 7.8 $\mu$ s (Tc  $\leq$  +85°C)

- Golden Contactor

- SDRAM Operation Temperature

- -40°C  $\leq$  TC  $\leq$  +85°C

- Programmable Device Operation:

- Burst Type: Sequential or Inteleave

- Operation: Burst Read and Write

- Device CAS# Latency: 3,4,5

- Burst Length: 4, 8

- RoHS Compliant (Section 14)

#### 2. Environmental Requirements

DDR2 W/T SODIMMs are intended for use in standard office environments that have limited capacity for heating and air conditioning.

| Symbol | Parameter                                 | Rating      | Units    | Notes |

|--------|-------------------------------------------|-------------|----------|-------|

| Topr   | Operating Temperature (ambient)           | -40 to +85  | °C       | 3     |

| Тѕтс   | Storage Temperature                       | -50 to +100 | °C       | 1     |

| Hopr   | Operating Humidity (relative)             | 10 to 90    | %        |       |

| Нѕтс   | Storage Humidity (without condensation)   | 5 to 95     | %        | 1     |

| PBAR   | Barometric Pressure (operating & storage) | 105 to 69   | K Pascal | 1,2   |

<sup>1.</sup> Stresses greater than those listed may cause permanent damage to the device. This is a stress rating only, and device functional operation at or above the conditions indicated is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability. 2. Up to 9850 ft.

<sup>3.</sup> The component maximum case temperature (Tcase) shall not exceed the value specified in the DDR2 DRAM component specification.

<sup>\*</sup>Following JEDEC specifications.\*

# 3. Ordering Information

| DDR2 W/T SODIMM |         |          |              |           |         |     |  |  |  |  |  |

|-----------------|---------|----------|--------------|-----------|---------|-----|--|--|--|--|--|

| Part Number     | Density | Speed    | DIMM         | Number of | Number  | ECC |  |  |  |  |  |

| Part Number     | Density | Speed    | Organization | DRAM      | of rank |     |  |  |  |  |  |

| M2SK-2GMF6IJ5-M | 2GB     | PC2-5300 | 256M x64     | 16        | 2       | N/A |  |  |  |  |  |

# 4. Pin Configurations (Front side/Back side)

-x64 SODIMM

|     | Front |     |        |     |       |     |        |     |      | Ba  | ick    |     |       |     |       |

|-----|-------|-----|--------|-----|-------|-----|--------|-----|------|-----|--------|-----|-------|-----|-------|

| Pin | Name  | Pin | Name   | Pin | Name  | Pin | Name   | Pin | Name | Pin | Name   | Pin | Name  | Pin | Name  |

| 1   | VREF  | 51  | DQS2   | 101 | A1    | 151 | DQ42   | 2   | VSS  | 52  | DM2    | 102 | A0    | 152 | DQ46  |

| 3   | VSS   | 53  | VSS    | 103 | VDD   | 153 | DQ43   | 4   | DQ4  | 54  | VSS    | 104 | VDD   | 154 | DQ47  |

| 5   | DQ0   | 55  | DQ18   | 105 | A10   | 155 | VSS    | 6   | DQ5  | 56  | DQ22   | 106 | BA1   | 156 | VSS   |

| 7   | DQ1   | 57  | DQ19   | 107 | BA0   | 157 | DQ48   | 8   | VSS  | 58  | DQ23   | 108 | /RAS  | 158 | DQ52  |

| 9   | VSS   | 59  | VSS    | 109 | /WE   | 159 | DQ49   | 10  | DM0  | 60  | VSS    | 110 | /S0   | 160 | DQ53  |

| 11  | /DQS0 | 61  | DQ24   | 111 | VDD   | 161 | VSS    | 12  | VSS  | 62  | DQ28   | 112 | VDD   | 162 | VSS   |

| 13  | DQS0  | 63  | DQ25   | 113 | /CAS  | 163 | NC     | 14  | DQ6  | 64  | DQ29   | 114 | ODT0  | 164 | CK1   |

| 15  | VSS   | 65  | VSS    | 115 | /S1   | 165 | VSS    | 16  | DQ7  | 66  | VSS    | 116 | A13   | 166 | /CK1  |

| 17  | DQ2   | 67  | DM3    | 117 | VDD   | 167 | /DQS6  | 18  | VSS  | 68  | /DQS3  | 118 | VDD   | 168 | VSS   |

| 19  | DQ3   | 69  | NC     | 119 | ODT1  | 169 | DQS6   | 20  | DQ12 | 70  | DQS3   | 120 | NC    | 170 | DM6   |

| 21  | VSS   | 71  | VSS    | 121 | VSS   | 171 | VSS    | 22  | DQ13 | 72  | VSS    | 122 | VSS   | 172 | VSS   |

| 23  | DQ8   | 73  | DQ26   | 123 | DQ32  | 173 | DQ50   | 24  | VSS  | 74  | DQ30   | 124 | DQ36  | 174 | DQ54  |

| 25  | DQ9   | 75  | DQ27   | 125 | DQ33  | 175 | DQ51   | 26  | DM1  | 76  | DQ31   | 126 | DQ37  | 176 | DQ55  |

| 27  | VSS   | 77  | VSS    | 127 | VSS   | 177 | VSS    | 28  | VSS  | 78  | VSS    | 128 | VSS   | 178 | VSS   |

| 29  | /DQS1 | 79  | CKE0   | 129 | /DQS4 | 179 | DQ56   | 30  | CK0  | 80  | CKE1   | 130 | DM4   | 180 | DQ60  |

| 31  | DQS1  | 81  | VDD    | 131 | DQS4  | 181 | DQ57   | 32  | /CKO | 82  | VDD    | 132 | VSS   | 182 | DQ61  |

| 33  | VSS   | 83  | NC     | 133 | VSS   | 183 | VSS    | 34  | VSS  | 84  | NC     | 134 | DQ38  | 184 | VSS   |

| 35  | DQ10  | 85  | NC/BA2 | 135 | DQ34  | 185 | DM7    | 36  | DQ14 | 86  | NC/A14 | 136 | DQ39  | 186 | /DQS7 |

| 37  | DQ11  | 87  | VDD    | 137 | DQ35  | 187 | VSS    | 38  | DQ15 | 88  | VDD    | 138 | VSS   | 188 | DQS7  |

| 39  | VSS   | 89  | A12    | 139 | VSS   | 189 | DQ58   | 40  | VSS  | 90  | A11    | 140 | DQ44  | 190 | VSS   |

| 41  | VSS   | 91  | A9     | 141 | DQ40  | 191 | DQ59   | 42  | VSS  | 92  | A7     | 142 | DQ45  | 192 | DQ62  |

| 43  | DQ16  | 93  | A8     | 143 | DQ41  | 193 | VSS    | 44  | DQ20 | 94  | A6     | 144 | VSS   | 194 | DQ63  |

| 45  | DQ17  | 95  | VDD    | 145 | VSS   | 195 | SDA    | 46  | DQ21 | 96  | VDD    | 146 | /DQS5 | 196 | VSS   |

| 47  | VSS   | 97  | A5     | 147 | DM5   | 197 | SCL    | 48  | VSS  | 98  | A4     | 148 | DQS5  | 198 | SA0   |

| 49  | /DQS2 | 99  | A3     | 149 | VSS   | 199 | VDDSPD | 50  | NC   | 100 | A2     | 150 | VSS   | 200 | SA1   |

#### 5. Architecture

#### Pin Definition

| Pin Name        | Description                 | Number | Pin Name   | Description           | Number |

|-----------------|-----------------------------|--------|------------|-----------------------|--------|

| CK[1:0]         | Clock Inputs, positive line | 2      | SA[1:0]    | SPD and TS address    | 2      |

| /CK[1:0]        | Clock inputs, negative line | 2      | DQ[63:0]   | Data Input/Output     | 64     |

| CKE[1:0]        | Clock Enables               | 2      | DM[7:0]    | Data Masks            | 8      |

| /RAS            | Row Address Strobe          | 1      | DQS[7:0]   | Data strobes          | 8      |

| /CAC            | California Address Charles  | 4      | /DOC[7:0]  | Data strobes          | 0      |

| /CAS            | Column Address Strobe       | 1      | /DQS[7:0]  | complement            | 8      |

|                 |                             |        |            | Logic Analyzer        |        |

| /WE             | Write Fachle                | 4      | TEST       | specific test pin     | 4      |

| /VVE            | Write Enable                | 1      | IESI       | (No connect on        | 1      |

|                 |                             |        |            | SO-DIMM)              |        |

| /S[1:0]         | Chip Selects                | 2      | VDD        | Core and I/O Power    | 12     |

| A[9:0],A[11:15] | Address Inputs              | 15     | VSS        | Ground                | 57     |

| A40 AD          | Address                     | 4      | VDEE       | Input/Output          | 4      |

| A10,AP          | Input/Autoprecharge         | 1      | VREF       | Reference             | 1      |

| BA[2:0]         | SDRAM Bank Address          | 3      | VDDSPD     | SPD and TS Power      | 1      |

|                 |                             |        |            | Reserved for optional |        |

| ODT[1:0]        | On-die termination control  | 2      | /Event Pin | hardware temperature  | 1      |

|                 |                             |        |            | sensing               |        |

|                 | Serial Presence Detect      |        |            | Reserved for future   |        |

| SCL             | (SPD) and Thermal           | 1      | NC         |                       | 3      |

|                 | sensor(TS) Clock Input      |        |            | use                   |        |

| SDA             | SPD and TS Data             | 1      |            | Total                 | 200    |

| SDA             | Input/Output                | 1      |            | Total:                | 200    |

# 6. Input/Output Functional Description

| Symbol     | Туре   | Polarity       | Function                                                                              |  |  |  |  |

|------------|--------|----------------|---------------------------------------------------------------------------------------|--|--|--|--|

|            |        |                | The system clock inputs. All address and command lines are sampled on the cross       |  |  |  |  |

| CK0 - /CK0 |        | Cross          | point of the rising edge of CK and falling edge of /CK. A Delay Locked Loop (DLL)     |  |  |  |  |

| CK1 - /CK1 | Input  | point          | circuit is driven from the clock inputs and output timing for read operations is      |  |  |  |  |

|            |        |                | synchronized to the input clock.                                                      |  |  |  |  |

|            |        |                | Activates the DDR2 SDRAM CK signal when high and deactivates the CK signal            |  |  |  |  |

| CKEI1.01   | lanut  | A ativa I liab | when low. By                                                                          |  |  |  |  |

| CKE[1:0]   | Input  | Active High    | deactivating the clocks, CKE low initiates the Power Down mode or the Self Refresh    |  |  |  |  |

|            |        |                | mode.                                                                                 |  |  |  |  |

|            |        |                | Enables the associated DDR2 SDRAM command decoder when low and disables               |  |  |  |  |

|            |        |                | the command                                                                           |  |  |  |  |

| /S[1:0]    | Input  | Active Low     | decoder when high. When the command decoder is disabled, new commands are             |  |  |  |  |

|            |        |                | ignored but previous operations continue. Rank 0 is selected by /S0; Rank 1 is        |  |  |  |  |

|            |        |                | selected by /S1.                                                                      |  |  |  |  |

| /RAS,      |        |                | When sampled at the cross point of the rising edge of CK and falling edge of CK       |  |  |  |  |

| /CAS, /WE  | Input  | Active Low     | and CAS,                                                                              |  |  |  |  |

| 70A0,7WE   |        |                | RAS, and WE define the operation to be executed by the SDRAM.                         |  |  |  |  |

| BA[2:0]    | Input  | _              | Selects which DDR2 SDRAM internal bank of four or eight is activated.                 |  |  |  |  |

| ODT[1:0]   | Input  | Active High    | Asserts on-die termination for DQ, DM, DQS, and /DQS signals if enabled via the       |  |  |  |  |

| 0.01[1.0]  | прис   | Active Flight  | DDR2 SDRAM mode register.                                                             |  |  |  |  |

|            |        |                | During a Bank Activate command cycle, defines the row address when sampled at         |  |  |  |  |

|            |        |                | the cross point of the rising edge of CK and falling edge of /CK. During a Read or    |  |  |  |  |

|            |        |                | Write command cycle, defines the column address when sampled at the cross point       |  |  |  |  |

|            |        |                | of the rising edge of CK and falling edge of /CK. In addition to the column address,  |  |  |  |  |

| A[9:0],    |        |                | AP is used to invoke autoprecharge operation at the end of the burst read or write    |  |  |  |  |

| A10/AP,    | Input  | _              | cycle. If AP is high, autoprecharge is selected and BA0-BAn defines the bank to be    |  |  |  |  |

| A[15:11]   |        |                | precharged. If AP is low, autoprecharge is disabled. During a Precharge command       |  |  |  |  |

|            |        |                | cycle, AP is used in conjunction with BA0-BAn to control which bank(s) to             |  |  |  |  |

|            |        |                | precharge. If AP is high, all banks will be precharged regardless of the state of     |  |  |  |  |

|            |        |                | BA0-BAn inputs. If AP is low, then BA0-BAn are used to define which bank to           |  |  |  |  |

|            |        |                | precharge.                                                                            |  |  |  |  |

| DQ[63:0]   | In/Out | _              | Data Input/Output pins.                                                               |  |  |  |  |

|            |        |                | The data write masks, associated with one data byte. In Write mode, DM operates       |  |  |  |  |

| DM[7:0]    | Input  | Active High    | as a byte mask by allowing input data to be written if it is low but blocks the write |  |  |  |  |

|            |        |                | operation if it is high. In Read mode, DM lines have no effect.                       |  |  |  |  |

| DQS[7:0],<br>/DQS[7:0] | In/Out             | Cross<br>point | The data strobes, associated with one data byte, sourced with data transfers. In Write mode, the data strobe is sourced by the controller and is centered in the data window. In Read mode, the data strobe is sourced by the DDR2 SDRAMs and is sent at the leading edge of the data window. /DQS signals are complements, and timing is relative to the crosspoint of respective DQS and /DQS. If the module is to be operated in single ended strobe mode, all /DQS signals must be tied on the system board to VSS and DDR2 SDRAM mode registers programmed appropriately. |

|------------------------|--------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD,<br>VDDSPD,<br>VSS | Supply             | _              | Power supplies for core, I/O, Serial Presence Detect, Thermal sensor, and ground for the module.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| VREF                   | Supply             | _              | Reference voltage for SSTL18 inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SDA                    | In/Out             | _              | This is a bidirectional pin used to transfer data into or out of the SPD EEPROM or Thermal sensor. A resistor must be connected from the SDA bus line to VDDSPD on the system planar to act as a pull up.                                                                                                                                                                                                                                                                                                                                                                      |

| SCL                    | Input              | -              | This signal is used to clock data into and out of the SPD EEPROM and Thermal sensor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SA[1:0]                | Input              | _              | Address pins used to select the Serial Presence Detect base address.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| TEST                   | In/Out             | _              | The TEST pin is reserved for bus analysis tools and is not connected on normal memory modules (SO-DIMMs).                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| /Event                 | Wire-<br>OR<br>Out | Active Low     | The optional EVENT pin is reserved for use to flag critical module temperatures and is used in conjuction with a SPD temperture sensing option.                                                                                                                                                                                                                                                                                                                                                                                                                                |

8 Rev 1.1 **February 2018**

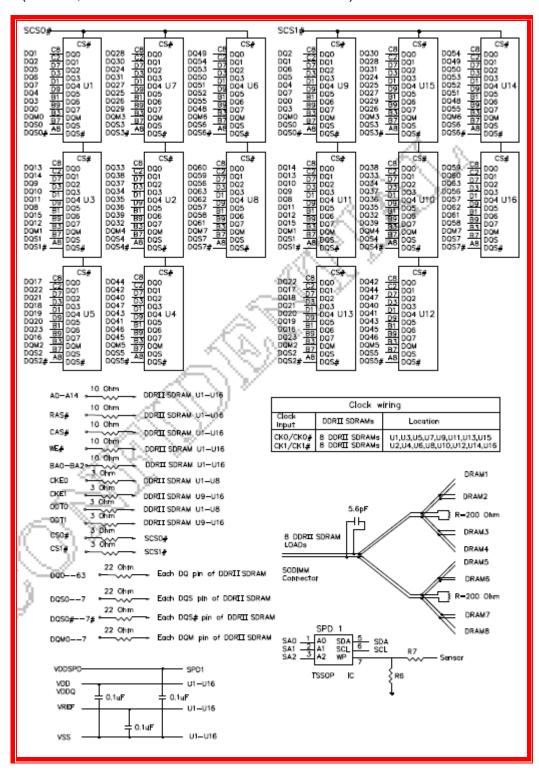

#### 7. Function Block Diagram:

- (2 Rank, 128Mx8 DDR2 base SDRAM Module)

#### 8. Absolute Maximum Ratings

| Symbol    | Parameter                           | Rating     | Units | NOTE |

|-----------|-------------------------------------|------------|-------|------|

| Vdd       | Voltage on VDD pin relative to Vss  | -1.0V~2.3V | V     | 1    |

| Vddq      | Voltage on VDDQ pin relative to Vss | -0.5V~2.3V | V     | 1    |

| VDDL      | Voltage on VDDL pin relative to Vss | -0.5V~2.3V | V     | 1    |

| VIN, VOUT | Voltage on any pin relative to Vss  | -0.5V~2.3V | V     | 1    |

#### NOTE:

- 1. Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- 2. Storage Temperature is the case surface temperature on the center/top side of the DRAM. For the measurement conditions, please refer to JESD51-2 standard.

- 3. VDD and VDDQ must be within 300mV of each other at all times; and VREF must be not greater than 0.6 x VDDQ. When VDD and VDDQ and VDDQ are less than 500mV, VREF may be equal to or less than 300mV.

- 4. Voltage on any input or I/O may not exceed voltage on VDDQ.

10 Rev 1.1 **February 2018**

#### 9. AC & DC Operating Conditions

#### 9.1 Recommended DC operating Conditions

| Sumbal | Parameter                    |           | Rating    |           |       |      |  |

|--------|------------------------------|-----------|-----------|-----------|-------|------|--|

| Symbol | Parameter                    | Min.      | Тур.      | Max.      | Units | NOTE |  |

| Vdd    | Supply Voltage               | 1.7       | 1.8       | 1.9       | V     |      |  |

| Vddl   | Supply Voltage for<br>DLL    | 1.7       | 1.8       | 1.9       | V     | 4    |  |

| VDDQ   | Supply Voltage for<br>Output | 1.7       | 1.8       | 1.9       | V     | 4    |  |

| Vref   | Input Reference<br>Voltage   | 0.49*VDDQ | 0.50*Vddq | 0.51*Vddq | mV    | 1,2  |  |

| Vтт    | Termination Voltage          | VREF-0.04 | VREF      | VREF+0.04 | V     | 3    |  |

NOTE: There is no specific device VDD supply voltage requirement for SSTL-1.8 compliance. However under all conditions VDDQ must be less than or equal to VDD.

- 1. The value of VREF may be selected by the user to provide optimum noise margin in the system. Typically the value of VREF is expected to be about 0.5 x VDDQ of the transmitting device and VREF is expected to track variations in VDDQ.

- 2. Peak to peak AC noise on VREF may not exceed +/-2% VREF(DC).

- 3. VTT of transmitting device must track VREF of receiving device.

- 4. AC parameters are measured with VDD, VDDQ and VDDL tied together.

#### 9.2 DRAM Operating Temperature Condition

| Symbol            | Parame                      | ter                | Rating    | Units | Note |

|-------------------|-----------------------------|--------------------|-----------|-------|------|

| T <sub>OPER</sub> | Operating Temperature Range | Normal Temperature | -40 to 85 | °C    | 1,2  |

#### Note:

- Operating Temperature TOPER is the case surface temperature on the center/top side of the DRAM.

- 2.  $T_{CASE} > 85^{\circ}C \rightarrow T_{REFI} = 3.9 \mu s$ . All DRAM specification only support  $0^{\circ}C < T_{CASE} < 85^{\circ}C$

#### 9.3 Input DC / AC Logic Level

| Symbol  | Parameter              | Min.       | Max.       | Units | Note |

|---------|------------------------|------------|------------|-------|------|

| Vıн(DC) | DC input logic<br>high | VREF+0.125 | Vddq+0.3   | V     |      |

| VIL(DC) | DC input logic low     | -0.3       | VREF-0.125 | V     |      |

11 Rev 1.1

| Vıн(AC) | AC input logic     | Vref+0.200 | -          | V | 1 |

|---------|--------------------|------------|------------|---|---|

| VIL(AC) | AC input logic low | -          | VREF-0.200 | V | 1 |

#### NOTE:

1. For information related to VPEAK value, Refer to overshoot/undershoot specification in device operation and timing datasheet; maximum peak amplitude allowed for overshoot and undershoot.

#### 9.4 AC Input Test Conditions

| Symbol      | Condition                               | Value    | Units | NOTE |

|-------------|-----------------------------------------|----------|-------|------|

| Vref        | Input reference voltage                 | 0.5*Vddq | V     | 1    |

| Vswing(MAX) | Input signal maximum peak to peak swing | 1.0      | V     | 1    |

| SLEW        | Input signal minimum slew rate          | 1.0      | V/ns  | 2,3  |

#### NOTE:

- 1. Input waveform timing is referenced to the input signal crossing through the ViH/IL(AC) level applied to the device under test.

- 2. The input signal minimum slew rate is to be maintained over the range from VREF to VIH(AC) min for rising edges and the range from VREF to VIL(AC) max for falling edges as shown in the below figure.

- 3. AC timings are referenced with input waveforms switching from  $V_{IL}(AC)$  to  $V_{IH}(AC)$  on the positive transitions and  $V_{IH}(AC)$  to  $V_{IL}(AC)$  on the negative transitions.

12 Rev 1.1 **February 2018**

### 10. Operating, Standby, and Refresh Currents

- 2GB SODIMM (2Rank, 128Mx8 DDR2 SDRAMs)

| Symbol  | Parameter/Condition                                                                                                                                                                                                                     | PC2-5300 | Unit |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|

| I DD0   | Operating Current: one bank; active/precharge; tRC = tRC (MIN); tCK = tCK (MIN); DQ, DM, and DQS inputs changing twice per clock cycle; address and control inputs changing once per clock cycle                                        | 960      | mA   |

| l DD1   | Operating Current: one bank; active/read/precharge; Burst = 2; tRC = tRC (MIN); CL=2.5; tCK = tCK (MIN); IOUT = 0mA; address and control inputs changing once per clock cycle                                                           | 1120     | mA   |

| I DD2P  | Precharge Power-Down Standby Current: all banks idle; power-down mode; CKE $\leq$ VIL (MAX); tCK = tCK (MIN)                                                                                                                            | 160      | mA   |

| I dd2n  | Idle Standby Current: CS ≥ VIH (MIN); all banks idle; CKE ≥ VIH (MIN); tCK = tCK (MIN); address and control inputs changing once per clock cycle                                                                                        | 384      | mA   |

| l dd2Q  | Precharge Quiet Standby Current: All banks idle; is HIGH; CKE is HIGH; $t_{CK} = t_{CK~(MIN)}$ ; Other control and address inputs are stable, Data bus inputs are floating.                                                             | 384      | mA   |

| I DD3PF | Active Power-Down Current: All banks open; tCK = tCK (MIN), CKE is LOW; Other control and address inputs are STABLE, Data bus inputs are floating. MRS A12 bit is set to <b>low</b> (Fast Power-down Exit).                             | 448      | mA   |

| I DD3PS | Active Power-Down Current: All banks open; tCK = tCK (MIN), CKE is LOW; Other control and address inputs are STABLE, Data bus inputs are floating. MRS A12 bit is set to <b>high</b> (Slow Power-down Exit).                            | 320      | mA   |

| I dd3n  | Active Standby Current: one bank; active/precharge; CS ≥ VIH (MIN); CKE ≥ VIH (MIN); tRC = tRAS (MAX); tCK = tCK (MIN); DQ, DM, and DQS inputs changing twice per clock cycle; address and control inputs changing once per clock cycle | 480      | mA   |

| l dd4W  | Operating Current: one bank; Burst = 2; writes; continuous burst; address and control inputs changing once per clock cycle; DQ and DQS inputs changing twice per clock cycle; CL=2.5; tCK = tCK (MIN)                                   | 1840     | mA   |

| l dd4r  | Operating Current: one bank; Burst = 2; reads; continuous burst; address and control inputs changing once per clock cycle; DQ and DQS outputs changing twice per clock cycle; CL = 2.5; tCK = tCK (MIN); IOUT = 0mA                     | 1760     | mA   |

| I DD5   | Auto-Refresh Current: tRC = tRFC (MIN)                                                                                                                                                                                                  | 2400     | mA   |

| I DD6   | Self-Refresh Current: CKE ≤ 0.2V                                                                                                                                                                                                        | 112      | mA   |

| l dd7   | Operating Current: four bank; four bank interleaving with BL = 4, address and control inputs randomly changing; 50% of data changing at every transfer; tRC = tRC (min); IOUT = 0mA.                                                    | 2960     | mA   |

# 11. AC Timing Specifications

| On mark of |                                                                                              | PC2-5300             |                     | Unit |

|------------|----------------------------------------------------------------------------------------------|----------------------|---------------------|------|

| Symbol     | Parameter -                                                                                  |                      | Max.                |      |

| tAC        | DQ output access time from CK/CK#                                                            | -0.45                | +0.45               | ns   |

| tDQSCK     | DQS output access time from CK/CK#                                                           | -0.40                | +0.40               | ns   |

| tCH        | CK high-level width                                                                          | 0.45                 | 0.55                | tcĸ  |

| tCL        | CK low-level width                                                                           | 0.45                 | 0.55                | tcĸ  |

| tHP        | Minimum half clk period for any given cycle; defined by clk high (tch) or clk low (tcl) time | tCH<br>or<br>tCL     | -                   | tСК  |

| tcĸ        | Clock Cycle Time                                                                             | 3                    | 8                   | ns   |

| tDS        | DQ and DM input setup time(differential data strobe)                                         | 0.1                  | -                   | ns   |

| tDH        | DQ and DM input hold time(differential data strobe)                                          | 0.175                | -                   | ns   |

| tipw       | Input pulse width                                                                            | 0.6                  |                     | tcĸ  |

| tDIPW      | DQ and DM input pulse width (each input)                                                     | 0.35                 | -                   | tcĸ  |

| tHZ        | Data-out high-impedance time from CK/XK                                                      | -                    | tACmax              | ns   |

| tLZ(DQS)   | DQS low-impedance time from CK/XK                                                            | tACmin               | tACmax              | ns   |

| tLZ(DQ)    | DQ low-impedance time from CK/XK                                                             | 2t <sub>AC</sub> min | t <sub>AC</sub> max | ns   |

| tDQSQ      | DQS-DQ skew (DQS & associated DQ signals)                                                    | -                    | 0.24                | ns   |

| tQHS       | Data hold Skew Factor                                                                        | -                    | 0.34                | ns   |

| tQН        | Data output hold time from DQS                                                               | tHP -<br>tQHS        | -                   | ns   |

| tDQSS      | Write command to 1st DQS latching transition                                                 | -0.25                | +0.25               | tcĸ  |

| tDQSL,(H)  | DQS input low (high) pulse width (write cycle)                                               | 0.35                 | -                   | tcĸ  |

| tDSS       | DQS falling edge to CK setup time (write cycle)                                              | 0.2                  | -                   | tCK  |

| tDSH       | DQS falling edge hold time from CK (write cycle)                                             | 0.2                  | -                   | tcĸ  |

| tMRD       | Mode register set command cycle time                                                         | 2                    |                     | tcĸ  |

| twpst  | Write postamble                                                        | 0.40               | 0.60 | tCK |

|--------|------------------------------------------------------------------------|--------------------|------|-----|

| tWPRE  | Write preamble 0.35 -                                                  |                    | tcĸ  |     |

| tıH    | Address and control input hold time                                    |                    | -    | Ps  |

| tis    | Address and control input setup time                                   | 200                | -    | Ps  |

| trpre  | Read preamble                                                          | 0.90               | 1.10 | tcĸ |

| tRPST  | Read postamble                                                         | 0.40               | 0.60 | tcĸ |

| trrd   | Active bank A to Active bank B command                                 | 7.5                | -    | Ns  |

| tDelay | Minimum time clocks remains ON after CKE asynchronously drops Low      | tIS + tCK<br>+ tIH | -    | Ns  |

| trefi  | Average Periodic Refresh Interval<br>(85°C < T <sub>CASE</sub> ≤ 95°C) | 3.                 | 3.9  |     |

| UKETT  | Average Periodic Refresh Interval (0°C ≤ T <sub>CASE</sub> ≤ 85°C)     |                    | 7.8  |     |

| tOIT   | OCD drive mode output delay                                            | 0                  | 12   | Ns  |

| tCCD   | CAS# to CAS# delay                                                     | 2                  |      | tcĸ |

| twr    | Write recovery time without Auto-Precharge                             | 15                 | -    | Ns  |

| WR     | Write recovery time with Auto-Precharge                                | twr/tck            | -    | tcĸ |

| tDAL   | Auto precharge write recovery + precharge time                         | WR+tRP             | -    | tcĸ |

| twTR   | Internal write to read command delay                                   | 7.5                | -    | Ns  |

| tRTP   | Internal read to precharge command delay                               | 7.5                |      | Ns  |

| txsnr  | Exit self refresh to a Non-read command                                | tRFC+10            |      | Ns  |

| txsrd  | Exit self refresh to a Read command                                    | 200                |      | tcĸ |

| tXP    | Exit precharge power down to any Non- read command                     | 2                  | -    | tCK |

| txard  | Exit active power down to read command                                 | 2                  | -    | tCK |

| txards | Exit active power down to read command                                 | 7-AL               |      | tCK |

| tCKE   | CKE minimum pulse width                                                | 3                  |      | tcĸ |

| Complete | Parameter                       | PC2-5300        |                      | 1124 |

|----------|---------------------------------|-----------------|----------------------|------|

| Symbol   |                                 | Min.            | Max.                 | Unit |

| taond    | ODT turn-on delay               | 2               | 2                    | tcĸ  |

| taon     | ODT turn-on                     | tAC (min)       | tAC (max)<br>+0.7    | Ns   |

| taonpd   | ODT turn-on (Power down mode)   | tAC (min)<br>+2 | 2tCK + tAC(max) +1   | Ns   |

| tAOFD    | ODT turn-off delay              | 2.5             | 2.5                  | tcĸ  |

| tAOF     | ODT turn-off                    | tAC(min)        | tAC(max)<br>+0.6     | Ns   |

| tAOFPD   | ODT turn-off (Power down mode)  | tAC<br>(min)+2  | 2.5tCK + tAC(max) +1 | Ns   |

| tanpd    | ODT to power down entry latency | 3               |                      | tCK  |

| taxpd    | ODT power down exit latency     | 8               |                      | tCK  |

# 12. Speed Grade Definition

| Complead | B                  | PC2- | 11-24  |      |

|----------|--------------------|------|--------|------|

| Symbol   | Parameter          | Min  | Max    | Unit |

| tRAS     | Row Active Time    | 45   | 70,000 | ns   |

| tRC      | Row Cycle Time     | 60   | -      | ns   |

| tRCD     | RAS to CAS delay   | 15   | -      | ns   |

| tRP      | Row Precharge Time | 15   | -      | ns   |

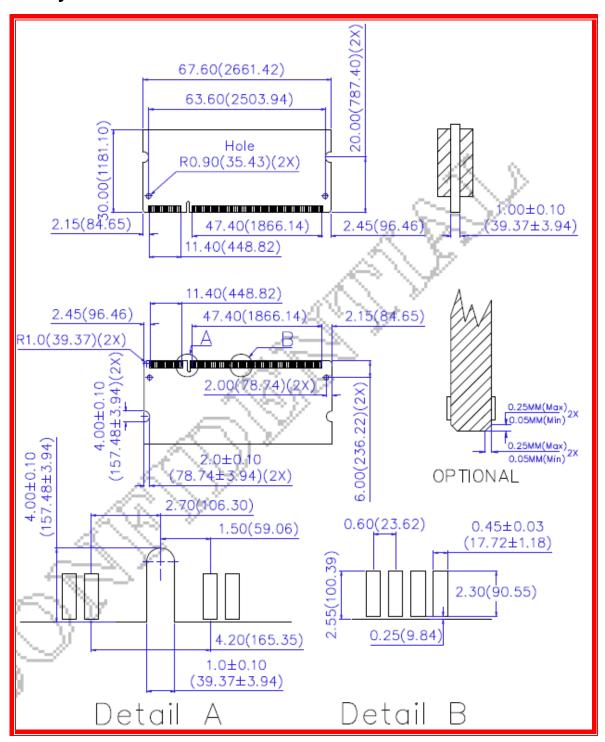

#### 13. Physical Dimension

Note: All dimensions are in millimeters (mils) and should be kept within a tolerance of  $\pm 0.15$  (6), unless otherwise specified.

#### 14. RoHS Declaration

innodisk

#### 宜鼎國際股份有限公司

Page 1/1

#### Innodisk Corporation

Tel:(02)7703-3000 Fax:(02) 7703-3555 Internet: http://www.innodisk.com/

#### ROHS 自我宣告書(RoHS Declaration of Conformity)

#### Manufacturer Product: All Innodisk EM Flash and Dram products

一、宜鼎國際股份有限公司(以下稱本公司)特此保證售予費公司之所有產品,皆符合歐盟 2011/65/EU及(EU) 2015/863 關於 RoHS 之規範要求。

Innodisk Corporation declares that all products sold to the company, are complied with European Union RoHS Directive (2011/65/EU) and (EU) 2015/863 requirement.

二、本公司同意因本保證書或與本保證書相關事宣有所爭議時,雙方宣友好協商,達成協議。

Innodisk Corporation agrees that both parties shall settle any dispute arising from or in connection with this Declaration of Conformity by friendly negotiations.

| Name of hazardous substance | Limited of RoHS ppm (mg/kg) |

|-----------------------------|-----------------------------|

| 鉛 (Pb)                      | < 1000 ppm                  |

| 汞 (Hg)                      | < 1000 ppm                  |

| 鍋 (Cd)                      | < 100 ppm                   |

| 六價鉻 (Cr 6+)                 | < 1000 ppm                  |

| 多溴聯苯 (PBBs)                 | < 1000 ppm                  |

| 多溴二苯醚 (PBDEs)               | < 1000 ppm                  |

| 鄉苯二甲酸二(2-乙基己基)酯 (DEHP)      | < 1000 ppm                  |

| 鄰苯二甲酸丁酯苯甲酯 (BBP)            | < 1000 ppm                  |

| 鄰苯二甲酸二丁酯 (DBP)              | < 1000 ppm                  |

| 鄰苯二甲酸二異丁酯 (DIBP)            | < 1000 ppm                  |

|                             |                             |

立 保 醬 🛊 人 (Guarantor)

Company name 公司名稱: Innodisk Corporation 宜鼎國際股份有限公司

Company Representative 公司代表人: Randy Chien 簡川勝

Company Representative Title 公司代表人職稱: Chairman 董事長

Date 日期: 2017 / 01 / 18

18 Rev 1.1

# **Revision Log**

| Rev | Date                           | Modification                    |

|-----|--------------------------------|---------------------------------|

| 0.1 | 23 <sup>rd</sup> January 2017  | Preliminary Edition             |

| 1.0 | 23 <sup>rd</sup> January 2017  | Official Release                |

| 1.1 | 26 <sup>th</sup> February 2018 | Updated RoHS and Modified typos |